# ATLAS Phase 2 upgrade

### Khuram Tariq (IHEP, Beijing) On behalf of the ATLAS collaboration

23-25 September 2024

Institute of High Energy Physics Chinese Academy of Sciences

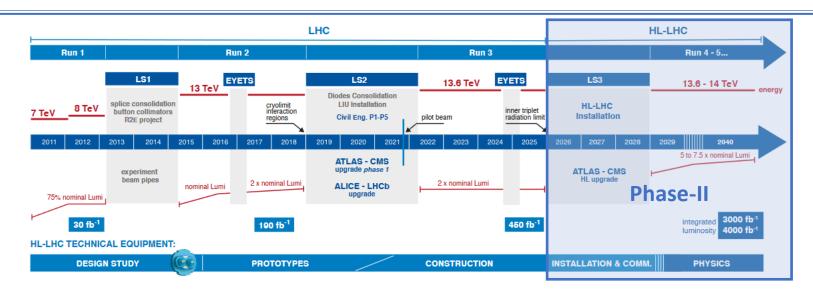

### The High Luminosity LHC

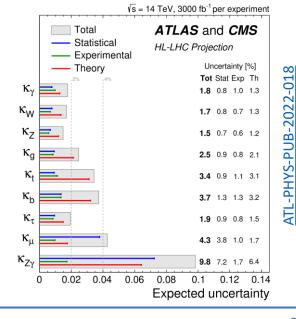

The HL-LHC program aims at collecting at least 3000 fb<sup>-1</sup> of 14 TeV pp collisions

This data will be essential to improve the knowledge of:

- Higgs couplings => uncertainty will be improved to $^{2}-4\%$ •

- Extend the searches for physics beyond the Standard model ٠

- More details in the talk physics prospects for HL-LHC ATLAS

#### The HL-LHC programs challenges the detector and detector electronics

Higher luminosity => from  $2x10^{34}$  cm<sup>-2</sup>s<sup>-1</sup> up to  $7.5x10^{34}$  cm<sup>-2</sup>s<sup>-1</sup>

Higher L1 trigger rates => from 100 kHz to 1 MHz

Higher pile-up conditions => from  $\langle \mu \rangle$ =55 up to  $\langle \mu \rangle$ =200

Increased radiation doses => about 20x increase up to a few MGy TID for 4000 fb-1

Major upgrades of all experiments needed to cope with these requirements!

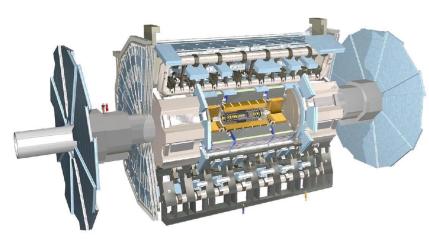

### ATLAS Phase-2 Upgrade

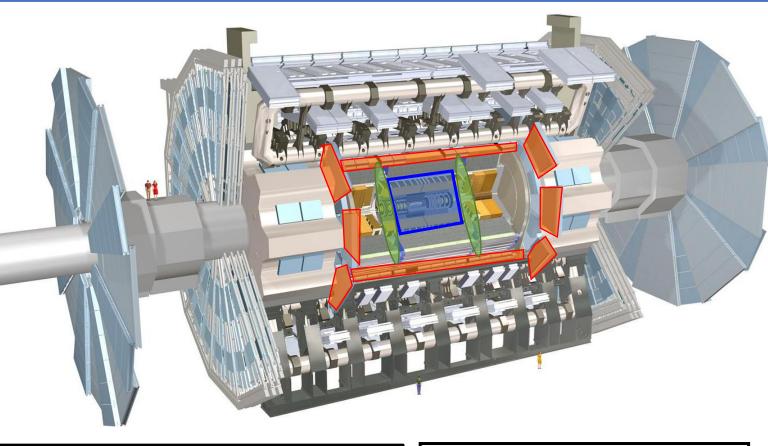

#### **New Inner Tracking Detector (ITk)**

- All silicon with 9 layers up to  $|\eta| = 4$

- Less material, finer segmentation

- Improve vertexing, tracking, b-tagging

### New High Granularity Timing Detector (HGTD)

- Precision track timing (30 ps) with LGAD in the forward region

- Improved pile-up separation and bunch-by-bunch luminosity

#### **Calorimeter Electronics**

- On-detector/off-detector electronics upgrades of LAr and Tile Calorimeter

- Provide 40 MHz readout for triggering

### **New Muon Chambers and electronics**

- Inner barrel region with new RPCs, sMDTs, and TGCs

- Improved trigger efficiency/momentum resolution, reduced fake rate

#### Upgraded Trigger and Data Acquisition System

- Single Level Trigger with 1 MHz output (x 10 current)

- Improved DAQ system with faster FPGAs

#### Additional small upgrades

- Luminosity detectors (1% precision)

- HL-ZDC (Heavy Ion physics)

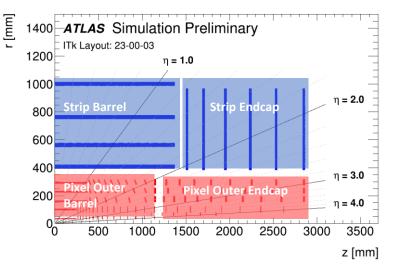

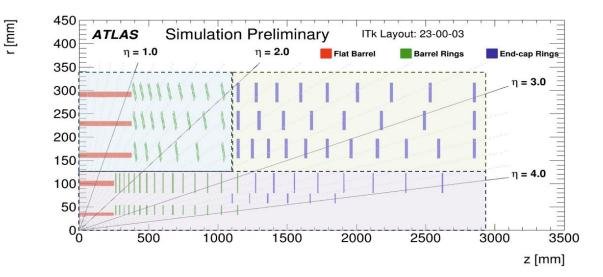

## A new tracker system, Inner Tracker(Itk)

### Full replacement of ATLAS tracking detectors with new all-silicon Inner Tracker (ITk)

- Extended tracking acceptance up to  $|\eta|=4$ :

- increased lepton reconstruction + jet flavour-tagging acceptance

- improved pile-up suppression

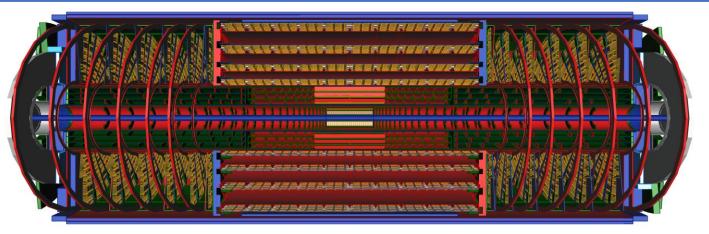

- Inner part made from 5 barrel layers and end-cap rings of pixel detectors, outer part made from 4 barrel layers and 6 end-cap disks of strip detectors

- Pixel: 13m<sup>2</sup> active area, 9400 modules, 1.4 giga-channels ٠

- Strips: 165m<sup>2</sup> active area, 17888 modules, 60 mega-channels

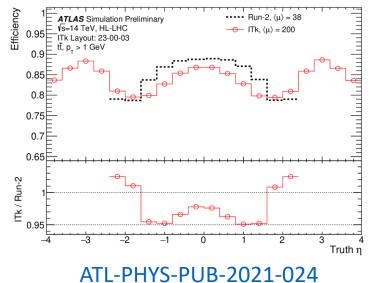

- Reduced material budget with respect to current ID

- Reduced fake rate even considering increased pileup

- Tracking performance comparable or better than before at much higher pile-up conditions

- $\geq$  13 hits/track in the barrel and  $\geq$  9 hits / track in the forward region

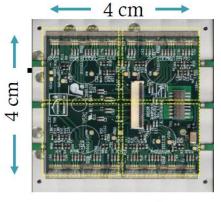

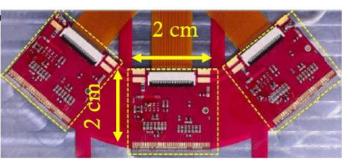

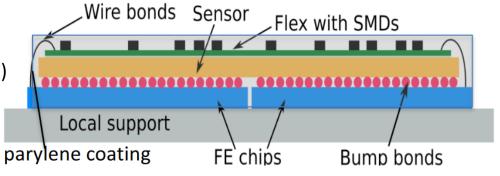

### The ITk Pixel Detector

quad module

triplet module

### Organized as three sub-systems (inner, outer barrel, outer endcaps)

- Inner system replaceable (radiation damage)

- Almost 10 times larger than current one in terms of area and number of modules

- Pixel sizes: 25x100  $\mu$ m<sup>2</sup> (innermost barrel layer only), 50x50  $\mu$ m<sup>2</sup> (everywhere else)

- 3D sensors in the innermost layer and planar sensors in the other layers

- Pre-production modules tested in test beams meet requirements after irradiation

- Sensor production is in progress

- ASIC production has been started

- Most of other components in pre-production phase

FE chip connected to the sensor by bump-bonds

## The ITk Strip Detector

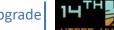

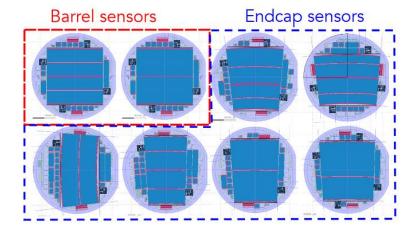

#### **Organized as two systems (Barrel and Endcaps):**

- Strip subsystem covering up to  $|\eta| < 2.7$  with 4 barrel layers, 6 end-cap disks

- Almost 3 times larger than current one in terms of area and 5 times as number of modules to be built

- Smaller strip lengths for better occupancy

- Radiation-tolerant up to fluences of 1.6×10<sup>15</sup>  $n_{eq}$ /cm<sup>2</sup> (expected max 5.4×10<sup>14</sup>  $n_{eq}$ /cm<sup>2</sup>

#### Short Strip Barrel module

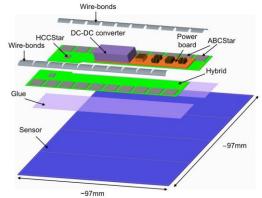

#### Status:

- ITk Strips is entering production for all components

- ASICs and sensors mostly delivered

- Mechanical sub-structures in pre-production

- Many system tests are ongoing

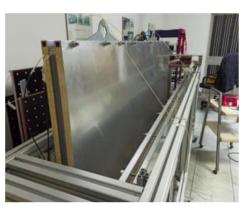

#### Barrel system test @ CERN

Endcap system test @ DESY

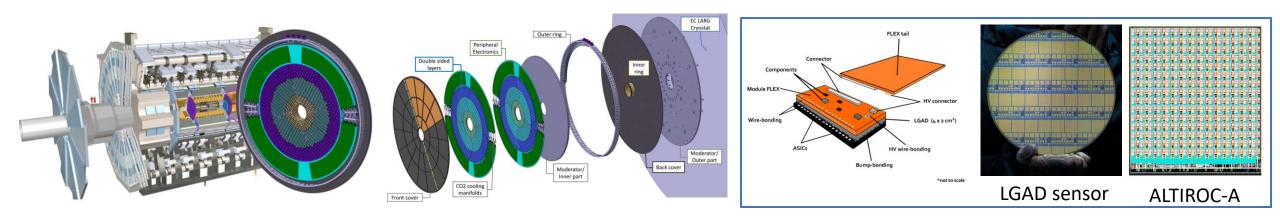

## High-Granularity Timing Detector

- Completely new detector between ITk and endcap calorimeter High Granularity Timing Detector (HGTD)

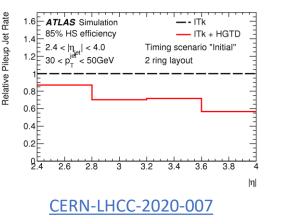

- Add time information to be combined with ITk position to improve pile-up rejection  $(2.4 < |\eta| < 4)$

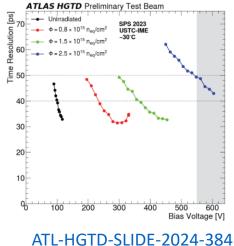

- Time resolution per hit of 35 ps and 70 ps after 2.5×10<sup>15</sup> n<sub>eq</sub>/cm<sup>2</sup> irradiation

### **Low gain avalanche detector (LGAD)** technology sensors, bump-bonded to read-out ASIC.

- Pre-production complete, performance matches design requirements

- Read-out ASIC (ALTIROC3) shows good performance

- First ALTIROCA and irradiated hybrids are being characterized at test beam

#### R&D coming to an end, moving towards mass production and construction of HGTD

#### Khuram Tariq (IHEP)

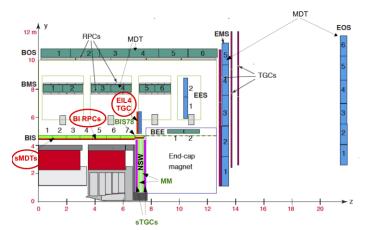

Upgrades of several types of muon chambers along with readout electronics and power systems upgrade

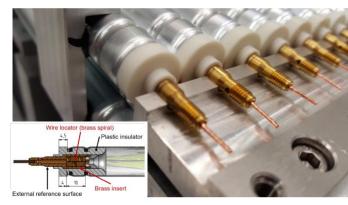

Improved trigger efficiency and momentum resolution, reduced fake rate **sMDT**

- Chamber production complete, High precision and performance

- ASICs are fully produced, Pre-production boards are being validated **RPC** (to improve trigger coverage)

- Mechanics design validated , Production is about to start

- ASICs submitted for production, Full validation of readout chain **TGC** (to improve trigger rejection)

- Chamber production started, Several chambers already done

- ASIC production completed, Moving towards board production

New sMDT chamber tubes

TGC EIL 4 prototype

**RPC prototype**

CERN-LHCC-2017-017

### Calorimeters upgrade

#### Electromagnetic calorimeter (LAr) **Tile Calorimeter Upgrade** Tile extended barrel Tile barre new radiation hard readout electronics, Replacement of on detector and off • providing precision readout of all calorimeter detector readout electronics LAr hadronic cells at 40 MHz end-cap (HEC) Replacement of LV and HV systems • Final designs for the off-detector Upgrade of calibration systems LAr electromagnetic • end-cap (EMEC) boards and firmware are underway New super-drawer mechanics Irradiation tests ongoing On schedule for installation into On-detector Off-detector 40 MHz LAr electromagnetic ATLAS cavern beginning in 2027 Detector Daughter board ENIC barrol DATA signals LAr forward (FCal) FireEl DCS DAO Σ 40 MHz Digital Trigger Sums AREUS Simulation Calibration Board Ar Timing System (LATS) EMB Middle $(\eta,\phi) = (0.5125, 0.0125)$ Level0 <µ> = 140, E<sup>true</sup> > 240 MeV ATLAS Preliminary Phase-II Upgrade - Median R7877 Front-End Board (FEB2 Tile Calorimeter LSTM (single) Daughter Boar LAr Signal Processor (LASP) New PMT° R11187 1.05 LSTM (sliding) I Ar Calorimeter Cells Adder B Vanilla-RNN (sliding) PMT 0.95 4-Conv CNN Current PMT 0.9 3-Conv CNN (underneath 0.85 OF with MaxFinder 0.8 0.6 0.4 0.2 0.8 100 200 300 400 500 $E_{T}^{pred}$ - $E_{T}^{true}$ [GeV] Integrated anode charge [C] **On Detector Off Detector** i.nima.2022.167595 ATL-LARG-PROC-2021-002

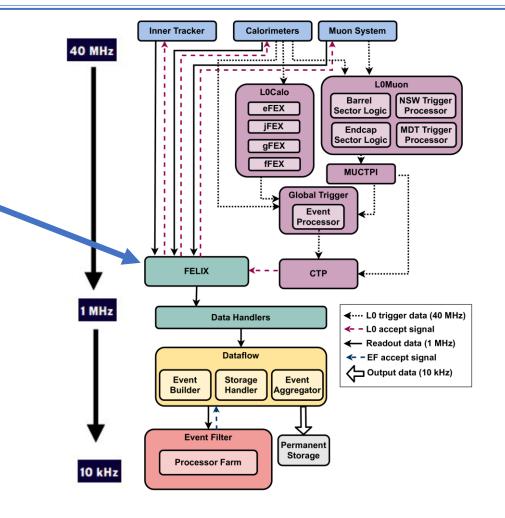

Huge increase in data rates and thus data throughput, bringing extra complexity!

#### DAQ:

• Completely new architecture based on custom FPGA cards (FELIX)

#### **Trigger:**

FELIX card Prototype: FLX-182

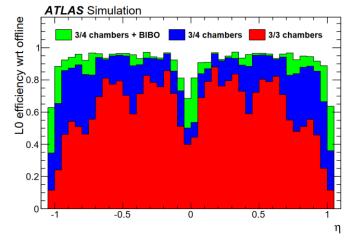

#### Hardware based Level-0:

- Trigger data input at 40 MHz from Calorimeters and Muons

- Output Rate 1 MHz (currently 100 kHz), latency 10 μs

- Exploits full detector granularity with new **Global Trigger component Software based Event Filter**:

- Output rate 10 kHz (currently 3 kHz)

- Extended tracking range fully exploiting ITk, improves muon trigger efficiency

- Accelerators (GPU), Machine Learning (ML) and Neural Networks (NN) for online reconstruction

#### New TDAQ architecture

- ATLAS has an ambitious upgrade program to fully exploit the physics potential of HL- LHC

- Upgrades are underway to provide better performance in a challenging environment such as high radiation doses and high pile-up

- New detectors and read-out electronics are being developed to ensure the high efficiency and highquality data taking in HL-LHC era

- Many projects are entering pre-production or production phase

- Schedule will also be a challenge, both for construction, as well for a compact installation during the next long LHC shutdown

With all these upgrades in place, ATLAS will be well prepared for many years of data taking at the high luminosity LHC!