# La mesure de temps haute-résolution de l'expérience LHCb avec l'asic SPIDER (Swift Pipelined Digitizer)

Ludovic Alvado, Nicolas Arveuf, Edouard Bechettoille,

*Christophe Beigbeder, Dominique Breton, Didier Charrier,*

*Raphael De Neef, Baptiste Joly,*

*Zülal Kiraz, Laurent Leterrier, Jihane Maalmi, Samuel Manen,*

*Hervé Mathez, Christophe Sylvia, Philippe Vallerand,*

Richard Vandaele

AG Pôle Ingénierie @ IJCLab - Orsay le 2 juin 2025

# Plan

- ✓ L'expérience LHCb en bref

- ✓ La jouvance phase II de l'Ecal de LHCb

- Motivations & besoin en mesure de temps haute resolution

- Spécifications de la nouvelle chaîne électronique

- ✓ Rappels

- La microélectronique et l'électronique

- Technologies / transistors

- ✓ L'ASIC SPIDER

- La mesure de temps haute résolution

- Principe

- Soumission du prototype

- Banc de tests

- ✓ Conclusion

# L'expérience LHCb en bref

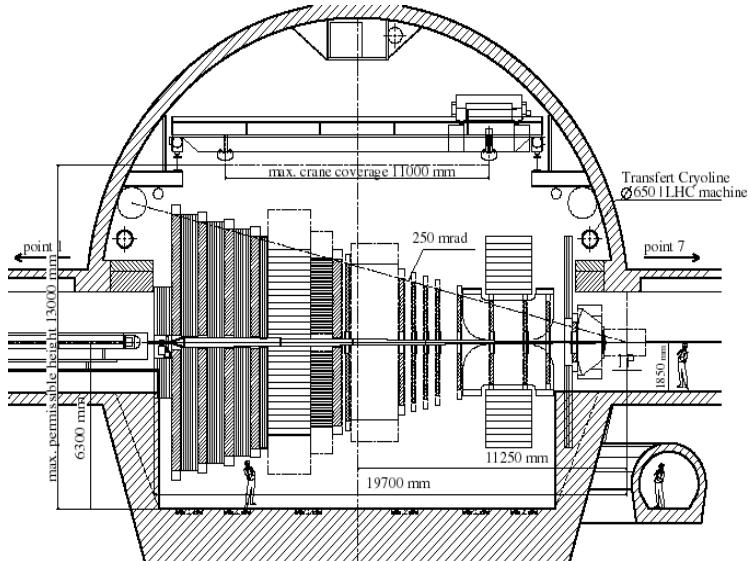

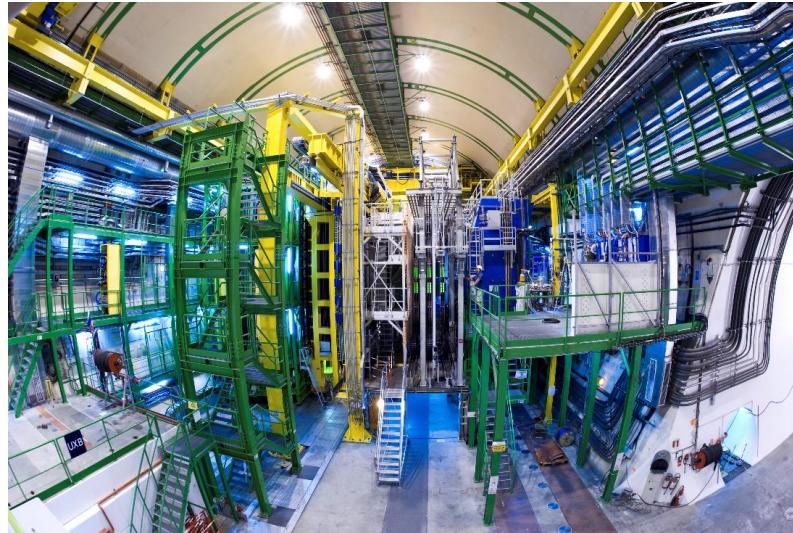

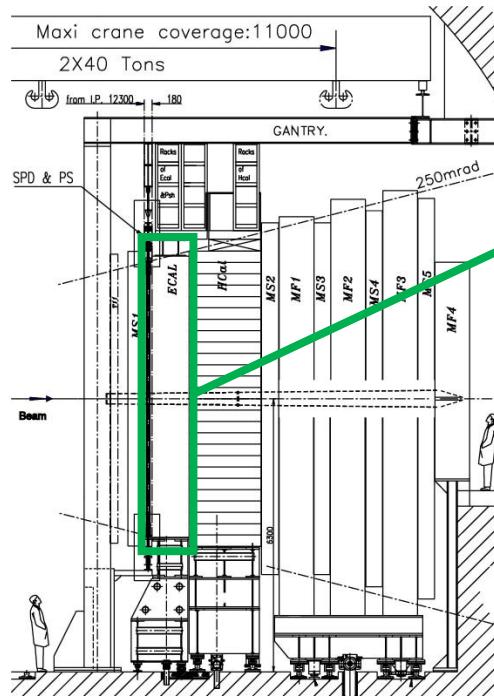

## ➤ Une des 4 grandes expériences du LHC depuis 2005

Coupe du détecteur dans la caverne

Détecteur & plateforme

- Les détecteurs HCAL et ECAL sont équipés de modules Shachlik pour les 1500 et 6000 voies d'acquisition.

- des câbles de 10 à 20m conduisent les signaux analogiques vers les ~ 250 cartes d'acquisition (Front-End Board)

- 10 baies et 18 châssis sont situés sur la plateforme au dessus du détecteur (radiation < 40 kRad)

- chaque châssis héberge une carte de contrôle (3CU), jusqu'à 16 cartes FEB et des cartes de calibration.

Mur de photomultiplicateurs

Front-End Board

Upgrade 1 2022

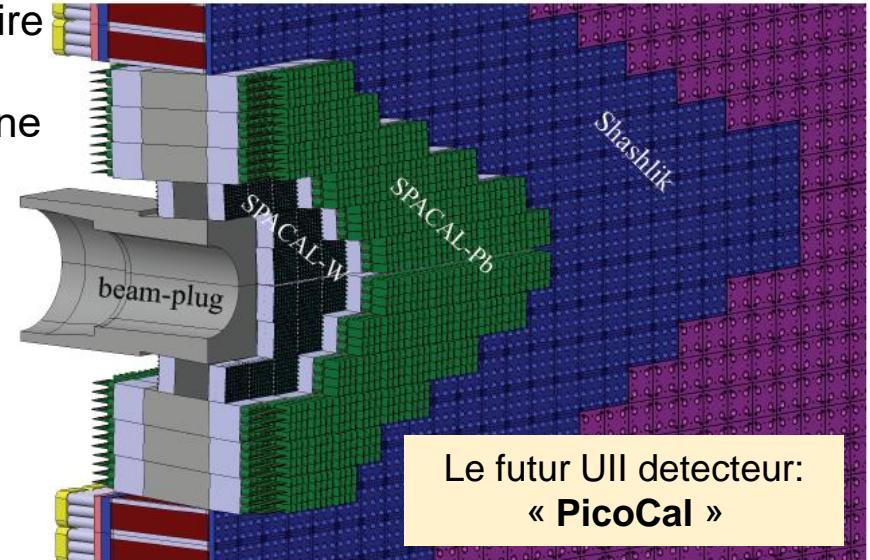

# La jouvence phase II du calorimètre électromagnétique de LHCb

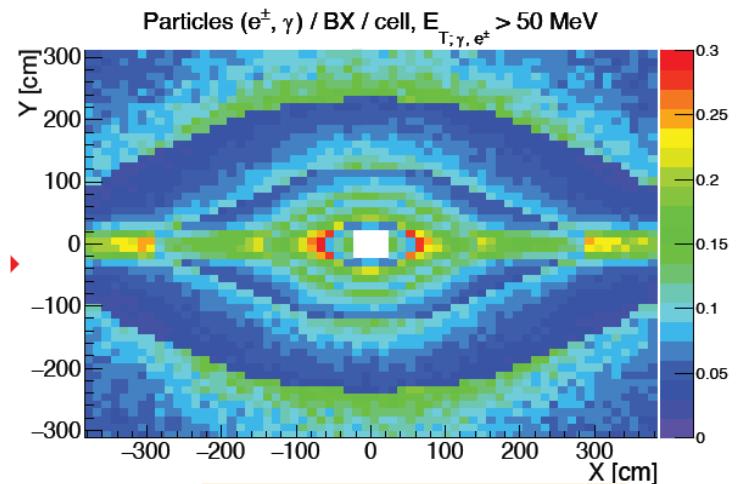

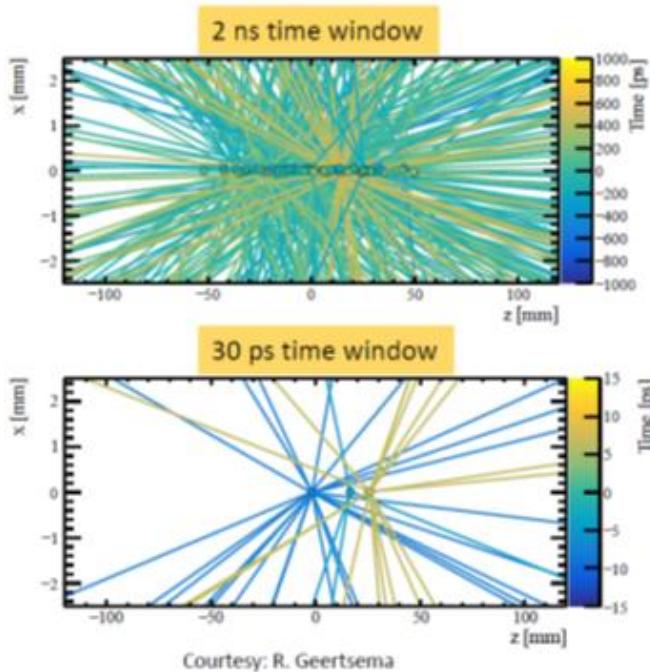

- Pourquoi cette jouvence phase II ? L'intensité des faisceaux « HL-LHC » va produire un nombre considérable d'événements qui vont s'empiler (35 fois plus à terme)

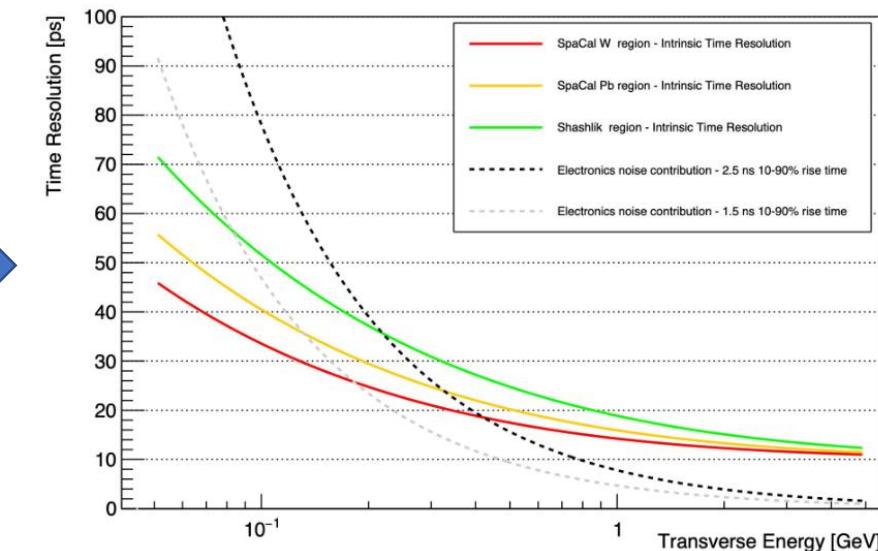

- Pour traiter ces empilements, le temps d'arrivée du signal doit être mesuré avec une résolution autour de 20 ps rms sur une gamme de 50MeV à 5GeV

UII detector occupancy

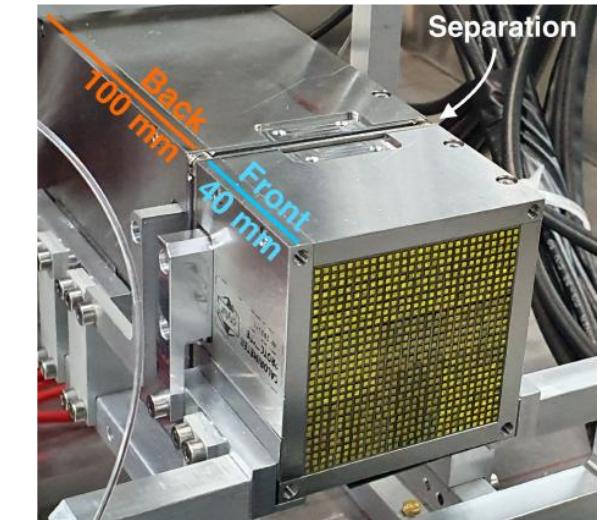

- Nouveaux types de détecteur : **module SPACAL pour la partie centrale (radiation <1MGy)** ; modules Shashlik pour la périphérie (< 40kGy),

- Nouvelle granularité de forme « rhomboic » : pour réduire le taux d'occupation par voie, la taille des modules sera réduite et donc le nombre de voies augmenté => ~30 000 voies d'acquisition

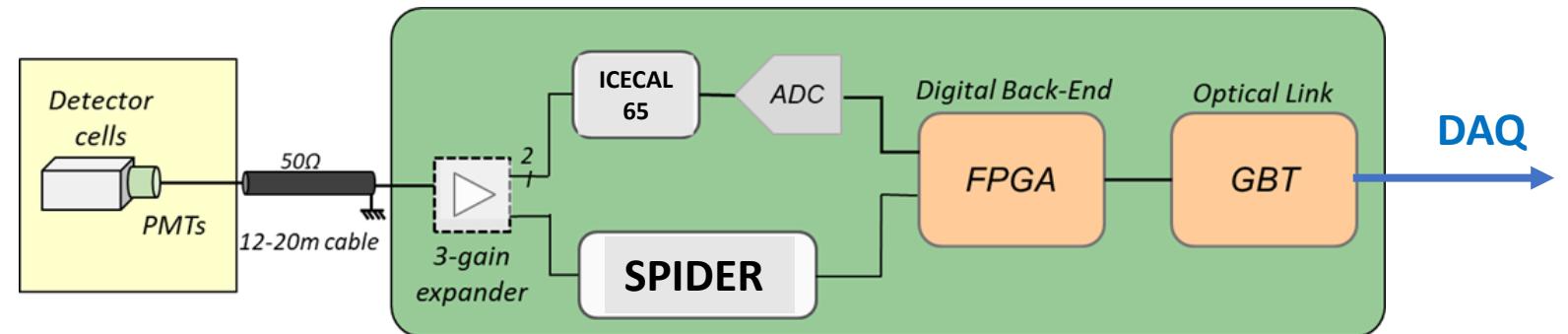

# La nouvelle chaîne de lecture du PicoCal

## ➤ Exigence de mesurer l'énergie et le temps d'arrivée des particules

### ➤ Mesure d'énergie

- Mesure périodique sur 12 bits à 40MHz

- Grande gamme dynamique de mesure : **50 MeV to 100 GeV**

- ASIC double gain **ICECAL65** (évolution de **ICECAL** avec 2 gains/voie)

### ➤ Mesure de temps - ASIC SPIIDER

- Mesure sélective par seuil : taux de comptage variable selon l'exposition de chaque cellule de détection, jusqu'à **10MHz max**

- Résolution en temps visée **15 ps pour  $E_T = [1-5 \text{ GeV}]$**  pour distinguer les interactions multiples

- Gamme de mesure de temps  **$E_T = [50 \text{ MeV} - 5 \text{ GeV}]$**

- Temps de montée des signaux entre **1.5 ns et 2.5 ns**

# La microélectronique

## ➤ Qu'est-ce que c'est ?

**Micro-électronique** ↔ **Electronique**

(Spécialité de l'électronique)

**circuit intégré**

(ASIC= Application Specific Integrated Circuit)

**carte électronique**

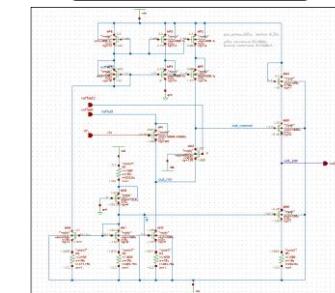

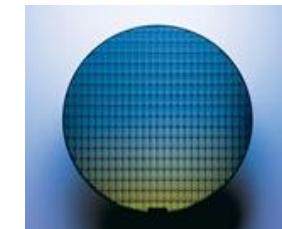

## ➤ De la conception à la fabrication des asics

**schémas**

**simulations**

**dessins des masques**

**fabrication**

**wafer**

**sciage**

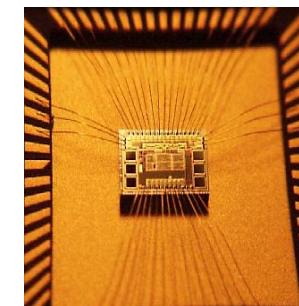

**puce ou « die »**

**« bonding »**

**puce mise en boîtier**

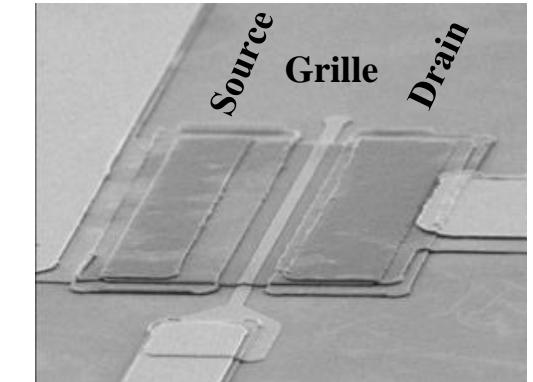

# Le transistor

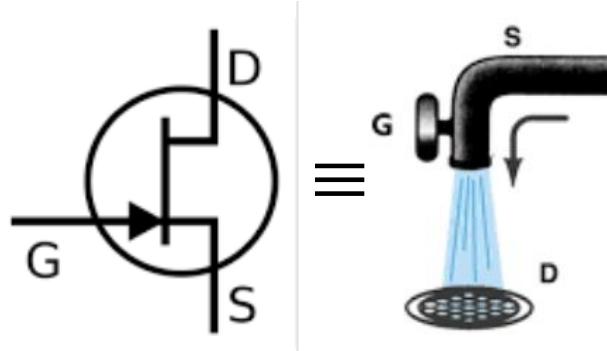

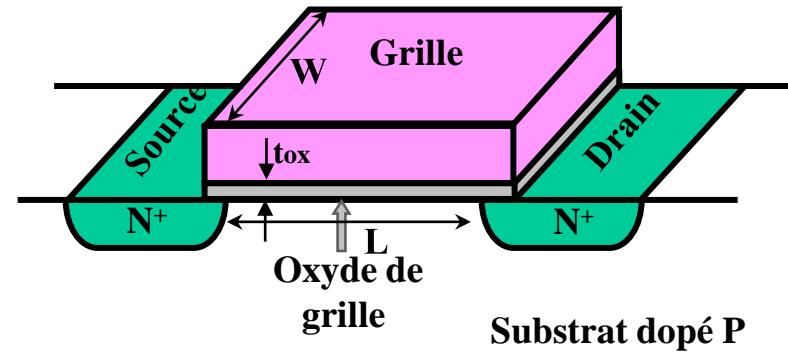

- L'élément de base en microélectronique. Dispositif semi-conducteur à 3 électrodes actives utilisé comme interrupteur ou amplificateur

Ex du transistor MOS

L : longueur de canal ; W : largeur de canal

transistor MOS

- Evolution technologique : diminution de la taille pour accroître la densité des asics

Réduction des dimensions :

• Longueur du canal : 45nm

• Épaisseur d'oxyde  $t_{ox}$  : 15Å

gains

- Réduction des tensions d'alimentation

- Réduction de la puissance dissipée

- Amélioration de la vitesse en  $1/L^2$

- gain :  $g_m \propto W/L$

- Vitesse :  $F_T = g_m/C \propto 1/L^2$

- Réduction des coûts

- Augmentation de la densité d'intégration

des milliards de transistors

sur une puce

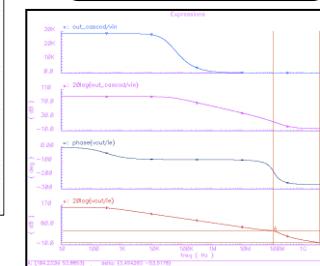

# Mesure de temps à haute résolution

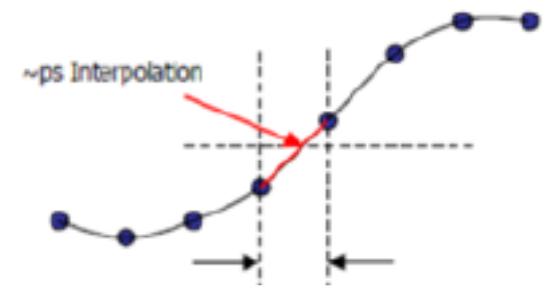

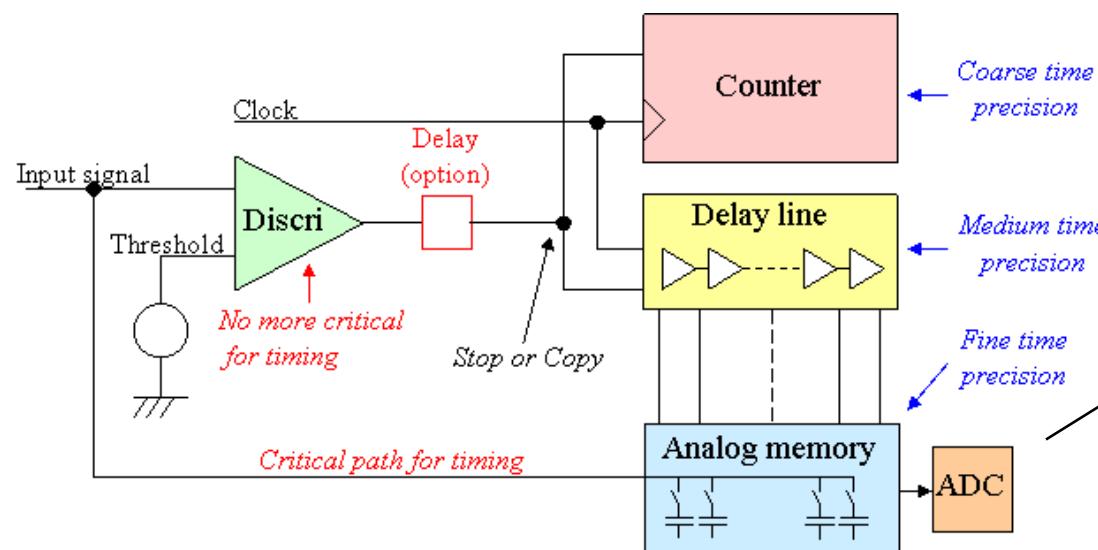

## ➤ Concept du « TDC à analyse de forme » = « Waveform Time to Digital Converter »

Concept breveté par LAL/IRFU en 2009 : association d'un TDC à DLL et d'un digitizer à base d'une mémoire analogique circulaire comme implémenté dans l'ASIC SAMPIC

Calcul du temps fin basé

sur un algorithme d'interpolation appelé :

« Discriminateur à fraction constante

numérique »

résolution obtenues de quelques

picosecondes RMS

- Un compteur donne le temps dit grossier du premier échantillon

- Une chaîne de retards donne la précision en temps des échantillons

- La numérisation du signal donne accès à la forme d'onde...

**Inconvénient majeur : limité à des taux de comptage de qq 100kHz,

temps mort important avec 1 seule banque mémoire**

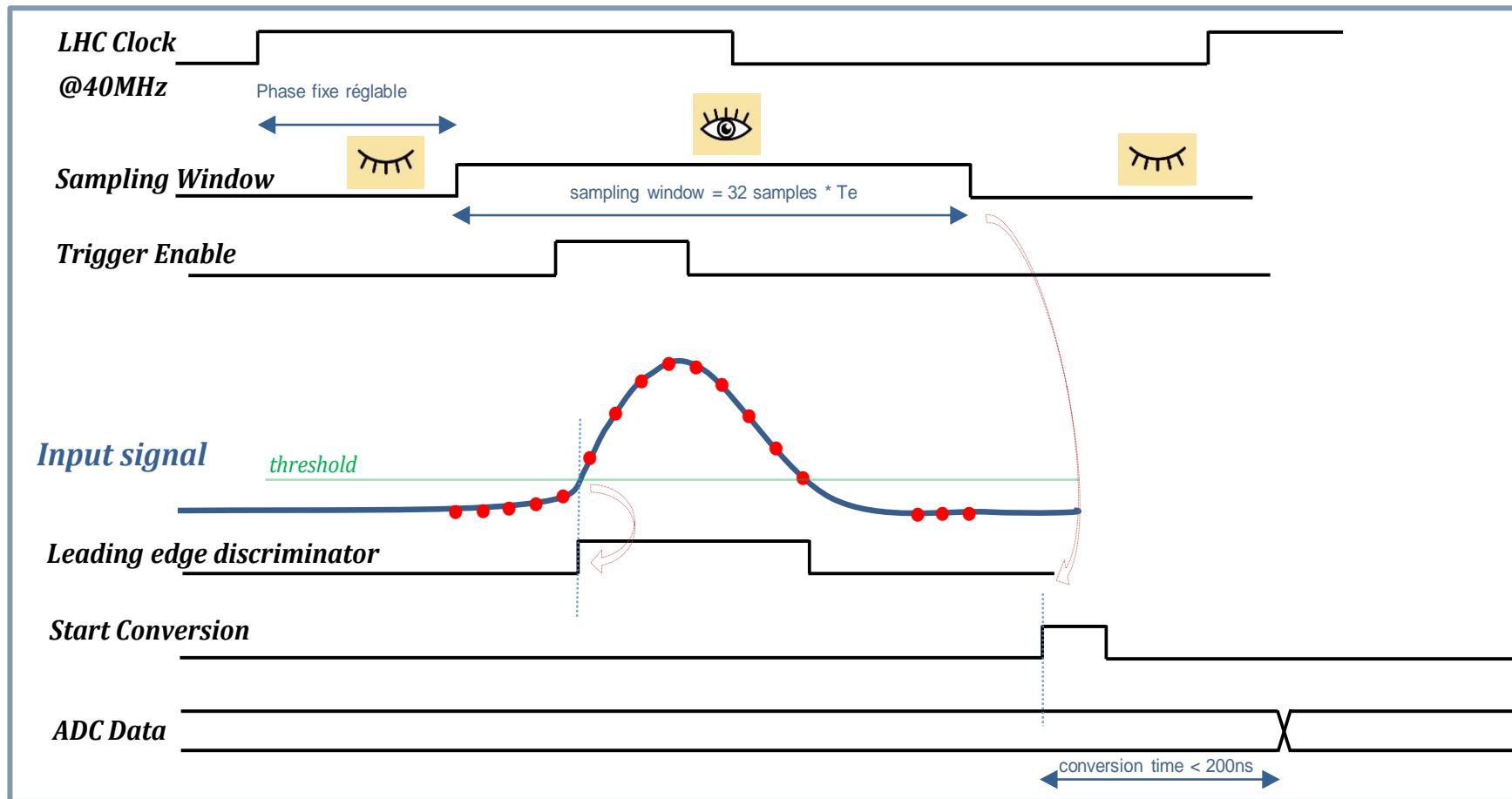

# Le principe de SPIDER

➤ Contrairement à une mémoire circulaire, **SPIDER est dédié aux collisionneurs et enregistre le signal à chaque croisement faisceau et durant une fraction de temps programmable**

- Possible car le temps de vol entre le vertex et chaque cellule de détecteur est prédictible

- Réduction du nombre de cellules mémoires par rapport à une mémoire circulaire

- Lecture “intelligente” permet de lire seulement les échantillons utiles

- Phases adjustables par rapport à l’horloge LHC :

- Fenêtre d’échantillonnage

- Fenêtre de validation du trigger

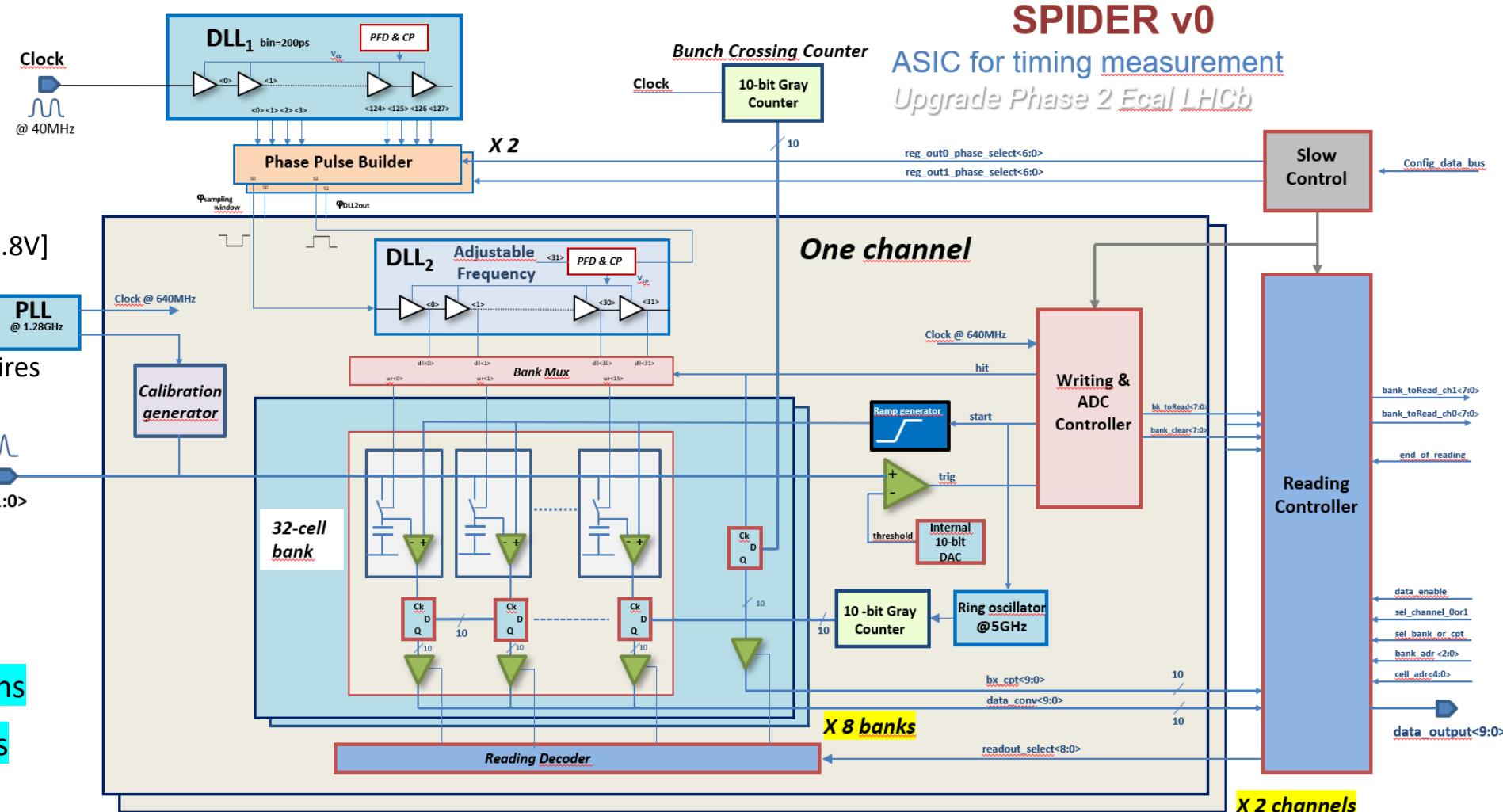

# La version prototype de SPIDER

## ➤ Spécifications de l'architecture du prototype de 2 voies (“V0”)

- TSMC 65nm, VDD 1.2V

- 2 voies auto-déclenchés

- Distribution d'horloge & DLL

- Cellule mémoire

- Etage de type “bootstrap”

- Bruit < 0.5 mV

- Système “Multi-banques”

- 8 banques de 32 cellules m

- Echantillonnage de 1.6 à 2

- ADC Wilkinson 10 bits@5 GHz

- Compteur rapide pour limiter le temps de conversion à 2

- PLL et DAC + buffer for calibration

- Bus commun de lecture de 16 bits

## Future version V1:

- 8 voies, lecture par lien série à 2.56 Gb/s par voie, ASIC-driven (mode “push”)

# La collaboration SPIDER

- “Projet R&T” @ IN2P3, 2021-2023 (RS: *P. Robbe* & RT: *C. Beigbeder*)

- Passage prévu en “master projet” à partir de fin 2025 : revue KDP @IN2P3 fin juin

- 5 laboratoires de l’IN2P3, co-coordinateurs pour le développement de SPIDER : *P. Vallerand & B. Joly*

- Organisation en 7 WPs

- Réunions bi-mensuelles

**Prototype soumis

début 2025 pour un

coût de 50k€**

N. Arveuf

G. Blanchard

B. Joly

F. Jouve

V. Tisserand

R. Vandaële

L. Alvado

L. Leterrier

E. Béchetoille

H. Mathez

D. Charrier

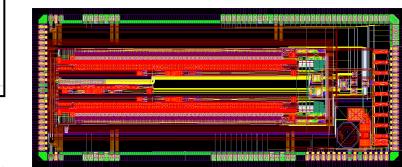

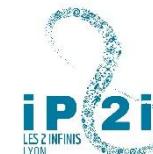

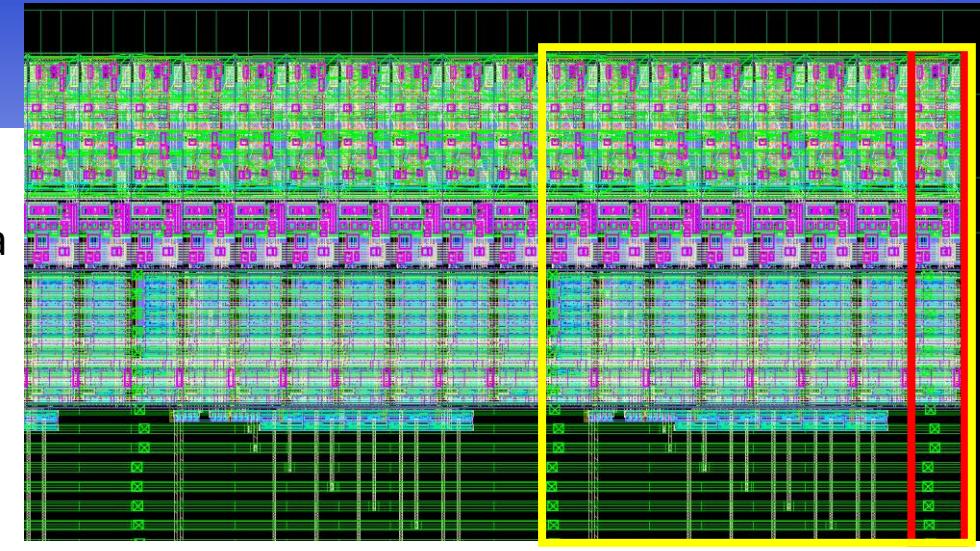

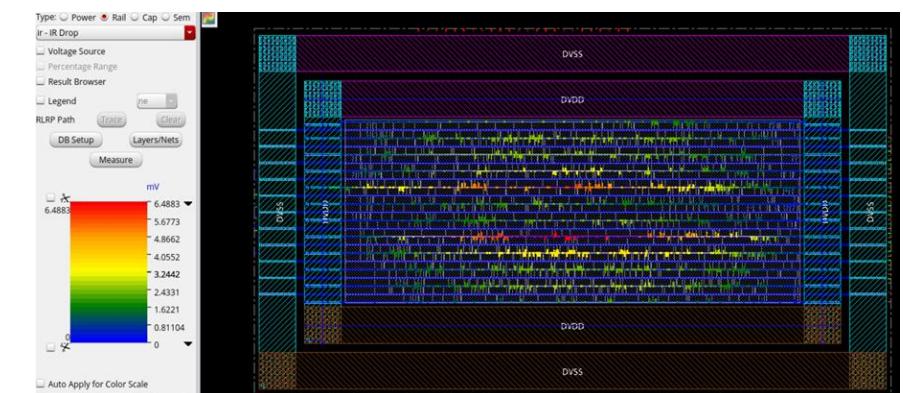

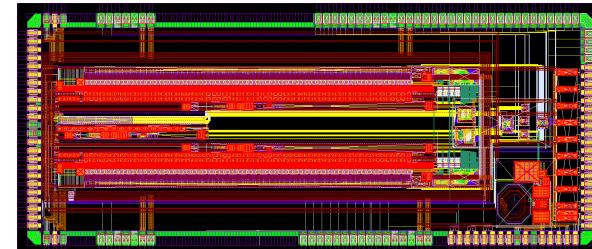

# Design du « Layout »

- Chaque voie est composée =>  $8 \times 32 = 256$  cellules d'échantillonnage

- Basé sur des pages où les 8 banques sont entrelacées. Longueur totale de la mémoire : 2,8 mm

- Distribution verticale des canaux avec de nombreux niveaux hiérarchiques.

- Notre philosophie : simulations post-layout approfondies pour vérifier : intégrité des signaux critiques, temporisation, couplages

- Optimisation pour réduire la consommation et les transitoires de courant sur les  $V_{DD}$

2 juin 2025

SPIDER – AG Pôle Ingénierie @ Orsay

page cell

- **V0 soumise début 2025: 2 x 5 mm<sup>2</sup>**

- **Premier tests prévus à partir de juin**

- **2 bancs de tests sont actuellement en cours de finalisation en parallèle @ IJCLab et LPC Clermont"**

12

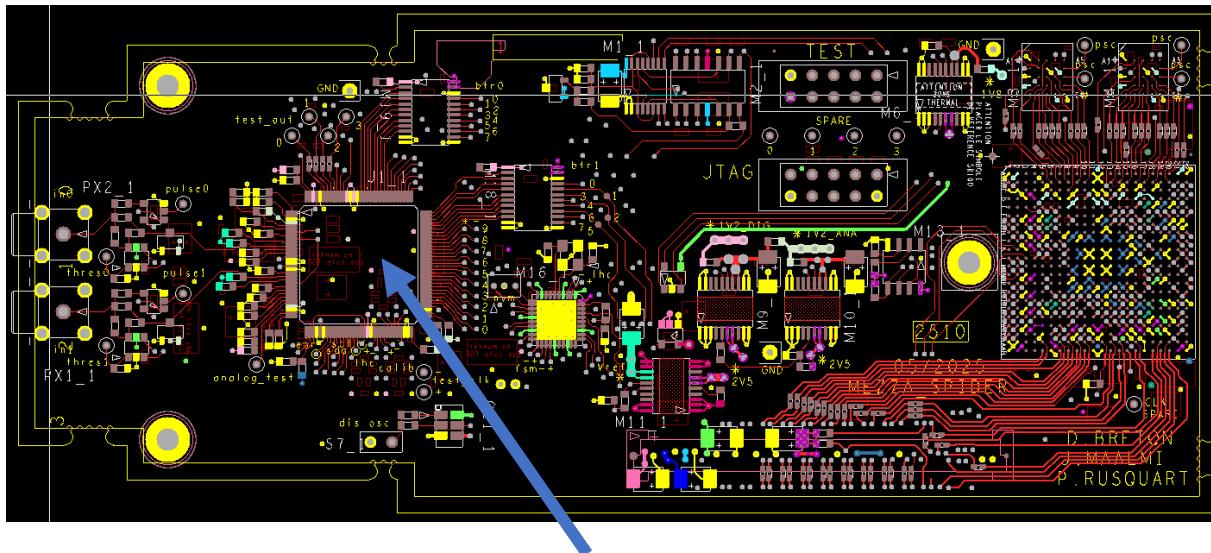

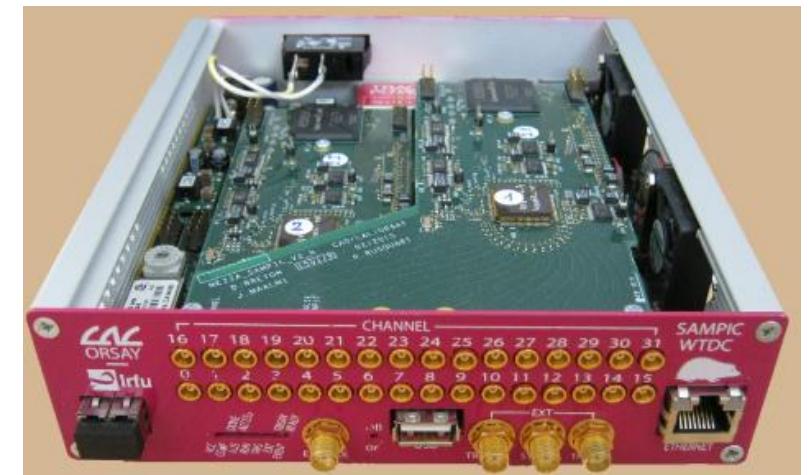

# Banc de tests de l'asic SPIDER

- Basé sur les modules de tests WaveCatcher et SAMPIC : association d'une carte mère avec toutes les interfaces + carte mezzanine dédiée

- Nous avons développé une nouvelle carte mezzanine pour accueillir Spider

- SPIDER sera encapsulé dans un boîtier de type QFP128 avec un pas de 400µm.

D. Breton

J. Maalmi

R. De Neeff

PCB carte mezzanine -SPIDER v0

Module de tests =

carte mère + carte mezzanine

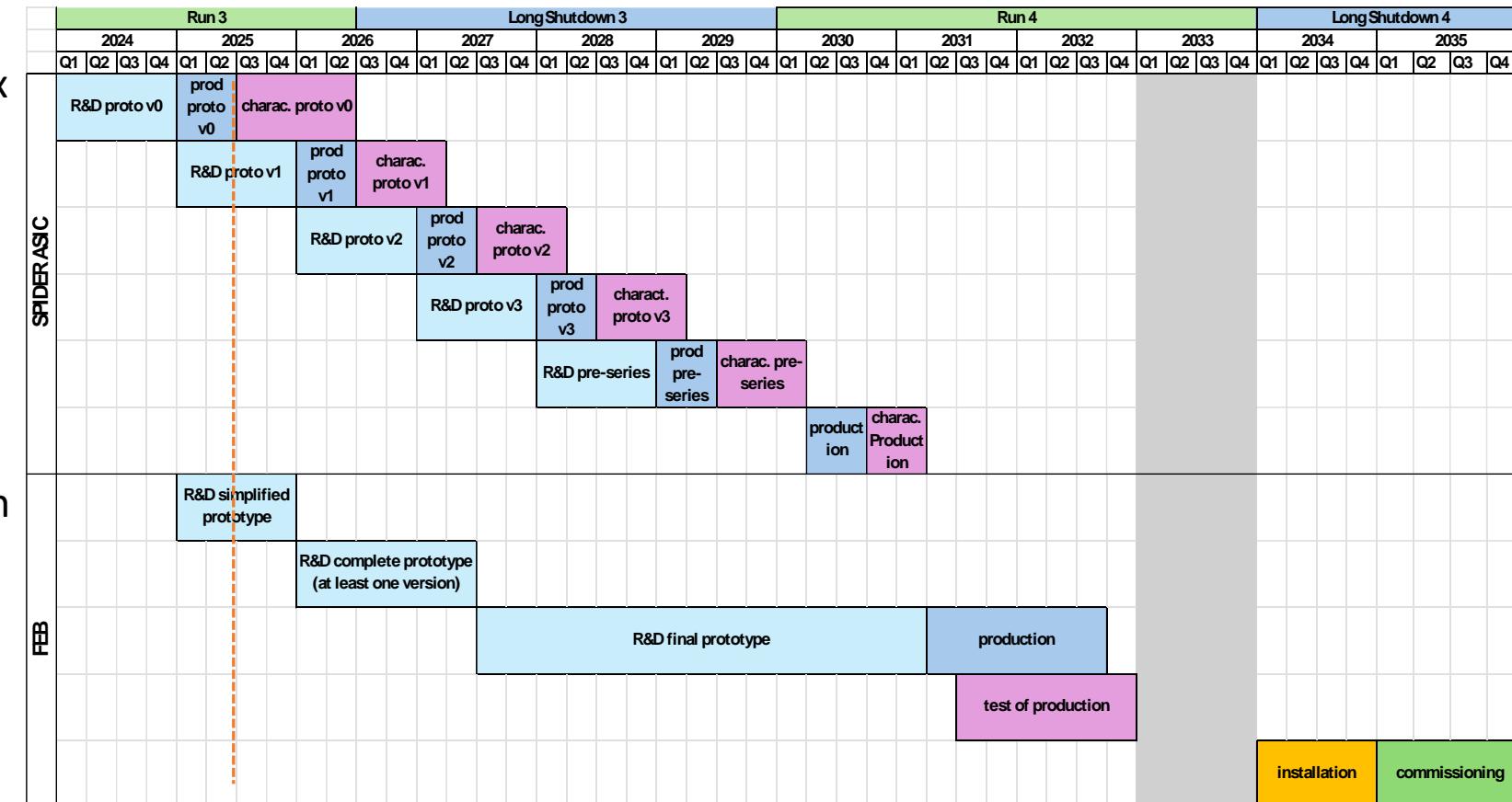

# Calendrier de développement

## ➤ Plan basé sur environ 1 cycle de fonderie par an de 2024 à 2029

soit 2 prototypes à 2 canaux et 3 prototypes à 8 canaux

- **SPIDER V0** (prototype à 2 canaux), conception 2023-2024, test 2025-2026

- **V0 bis** si nécessaire (prototype à 2 canaux avec corrections)

- **V1 (8 canaux)**

- **V2** (8 canaux + tolérance aux radiations + optimisations)

- **V3** (+ objectif de « rendement »)

- **2028** : test du V3 ; conception de la préproduction

- **2029** : caractérisation de la préproduction

- **2030** : production de SPIDER (30 000 canaux, production des cartes d'acquisition)

- **2031-2032** : production et test des cartes

- 2034 : installation

- 2035 : mise en service

# Conclusion

- La R&D des détecteurs progresse et se rapproche des objectifs visés en termes de résistance aux radiations et de performance temporelle.

- **La large gamme dynamique de mesure** sur la partie basse de la gamme d'énergie représentent **un double défi pour la mesure du temps**.

- Développement d'une **nouvelle architecture de SPIDER** à l'état de l'art optimisée pour:

- traitement des forts taux de comptage  $\sim 10\text{MHz}$

- capable de sélectionner les échantillons numériques pour rendre le flux de lecture des données supportable par l'acquisition

- SPIDER devrait être utilisable avec tout type de détecteur rapide sur un collisionneur à 40 MHz.

- L'échantillonnage peut aller jusqu'à 20 GS/s pour des signaux très rapides

- Pour **Picocal**, la meilleure résolution temporelle possible dépendra directement du temps de montée du signal

- Il reste encore beaucoup de chemin à parcourir...

- Mais c'est déjà un grand pas en avant !

# Merci de votre attention.