# Adrien HENROT

Dépt. Informatique - Développement

- Adrien Henrot

- Licence d'informatique (Paris Saclay)

- Master de Calcul Haute Performance (UVSQ)

- Stage de M1 (service développement)

- Contribution à une bibliothèque de structures de données pour le calcul (Kiwaku)

- Ajout d'un backend de calcul vectoriel (via la librairie EVE)

- Stage de M2 au LISN/IJCLab (service développement)

- Ajout du support de structures de stockage hiérarchique de donnée en C++ (Kiwaku)

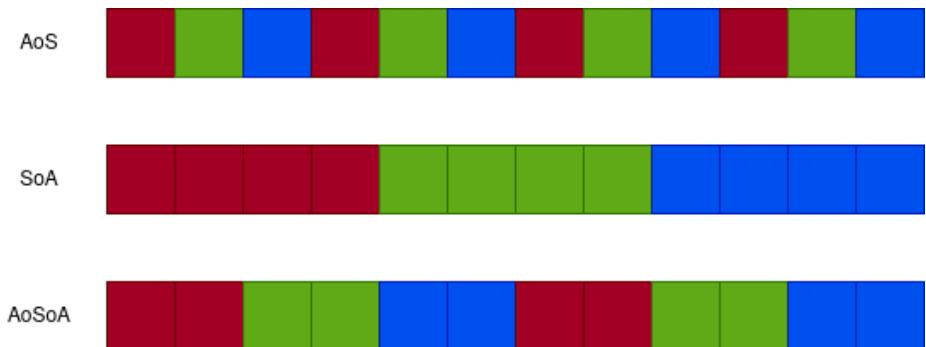

- Représentation en mémoire de collections d'objets

- Modification de l'organisation de données sans modification profonde du code

Représentation d'une liste de pixel (rgb) en mémoire

- En thèse avec David Chamont et Hadrien Grasland à IJCLab et Joël Falcou au LISN

- Problématique de représentation en mémoire de données hiérarchiques

- Comment bénéficier des hiérarchies mémoire des processeurs modernes (CPU/GPU)

- Comment bénéficier entièrement de leur capacité de calcul

- Utilisation du C++ moderne pour une interface souple

- Description haut niveau des structures/algorithmes

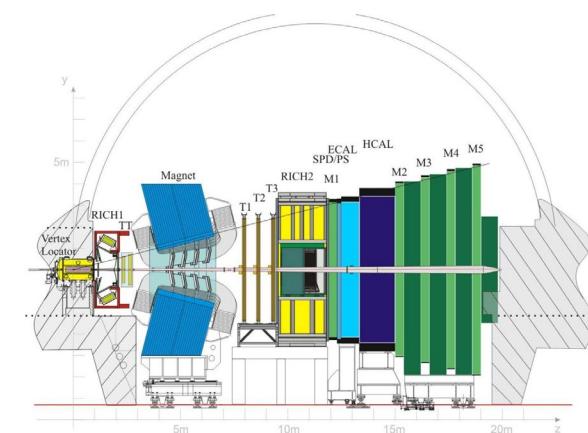

- Cas d'usage : LHCb

- Prochaine upgrade : 3 TB/s de données (~ 30MHz)

- Flux de données structurées à traiter en temps réel

- Vous pouvez me trouver au bâtiment 200 !

# Dmytro HOHOV

Dépt. DéTECTEURS et INSTRUMENTATION

**Parcours:**

- 2016 – 2019: **Thèse** à l'Université Paris-Saclay – **R&D de détecteurs à pixels** « *Avancées technologiques dans le domaine des pixels planaires pour l'expérience ATLAS Phase-2* »

- 2020 – 2022: **CDD** à IIHE (ULB, Bruxelles) – Production de **détecteurs à micropistes** pour le Phase-2 Tracker CMS

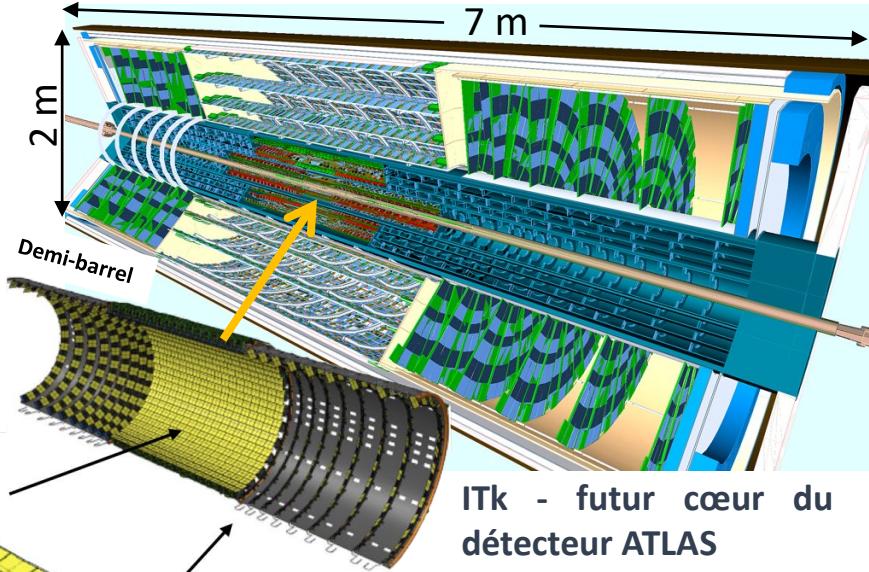

- 2022 – 2025: **CDD** à IJCLab – Production et contrôle qualité des **détecteurs à pixels** pour ATLAS Inner Tracker (ITk)

**Mon rôle au sein de IJCLab:**

- Ingénieur de recherche au **Département DéTECTEURS et INSTRUMENTATION associée**

- Spécialiste des **détecteurs en silicium**

- Conception, mise en œuvre et exploitation de bancs de test

- Caractérisation et contrôle qualité des modules à pixels

- Soutien à la production et analyse des performances des modules ITk

Moi avec le détecteur CMS au LHC ☺ - juillet 2019.

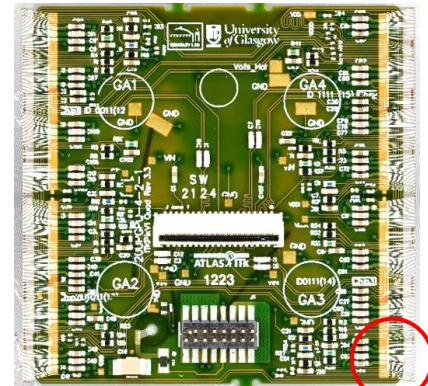

# Tests QC des modules pixels ITk assemblés à IJCLab

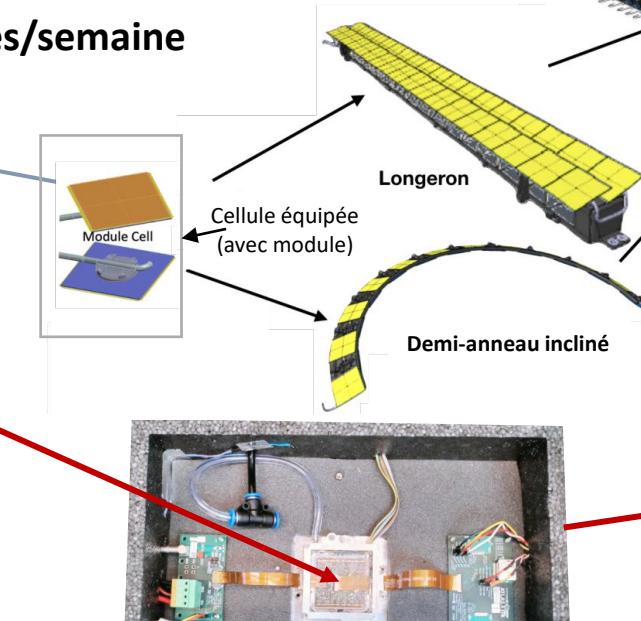

## Modules Pixels Quad production:

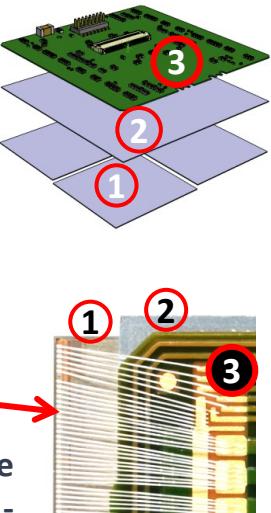

- 1 capteur connecté à 4 puces FE par **bump-bonding**

- Capteurs **planar n-in-p (150 µm)** + puce de lecture **ITkPixV2** (CERN RD53, 65 nm, pixels  $50 \times 50 \mu\text{m}^2$ , taux 3 GHz/cm $^2$ , trigger 1 MHz )

- Tolérance radiation :  $2 \times 10^{16} \text{ n}_{\text{eq}}/\text{cm}^2$

- Production collective (IJCLab, LPNHE, IRFU)  $\approx 2200$  modules  $\sim 33\%$  des modules du barrel externe

- Objectif de cadence nominale : **27 modules/semaine**

Module à pixels ITk: (1) - Puce de lecture; (2) - Capteur; (3) - Circuit imprimé flexible.

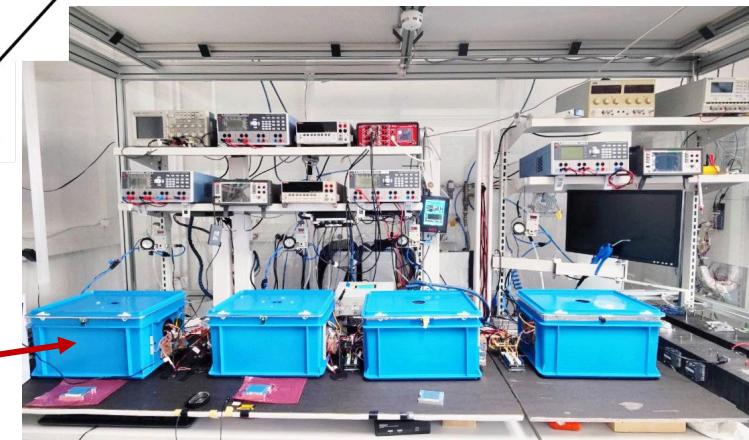

Boîte à température contrôlée.

Espace de tests QC des modules pixels ITk.

## Réunion du pôle Ingénierie : mes activités en 3mn

## Réunion du pôle Ingénierie : mes activités en 3mn

# Matias VECCHIO

Dépt. Informatique - Online

## Réunion du pôle Ingénierie : mes activités en 3mn

# Thomas ZERGUERRAS

Dépt. DéTECTEURS et INSTRUMENTATION

## Réunion du pôle Ingénierie: mes activités en 3mn

Thomas Zerguerras (Pôle Ingénierie – Service DéTECTEURS)

Arrivée à IJCLab : 01/10/2025

- **Contexte:** projet ANDROMEDE

- **Activités :** Développement d'un modèle IA pour analyse spectres TOF

Projet ANDROMEDE: instrument pour analyse de spectroscopie de masse avec faisceaux de nanoparticules

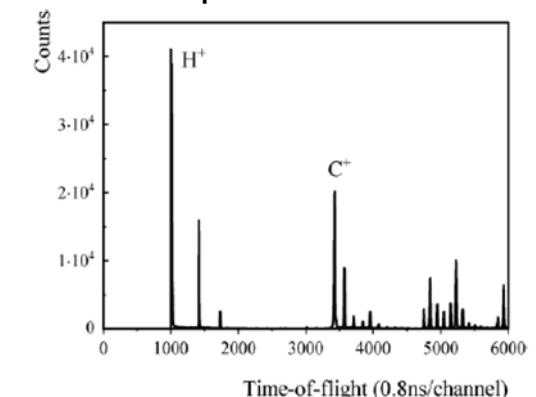

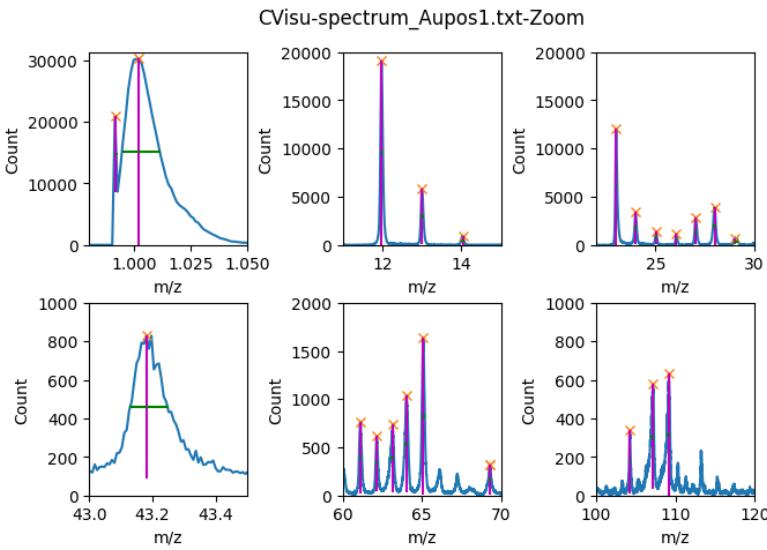

Spectre TOF

Développer un modèle IA pour l'analyse des spectres TOF

- En collaboration avec les chercheurs de la collaboration ANDROMEDE et le service Développement:

- Construire base de données (sources: spectres TOF expérimentaux calibrés)

- Implémenter modèle(s) IA

- Apprentissage modèle(s) sur données et validation

- Mise en œuvre sur « nouvelles » données

## Spectre TOF

## Base de données

## Réunion du pôle Ingénierie : mes activités en 3mn

# **Sid Ali CHERRATI**

**Dépt. Informatique - Online**

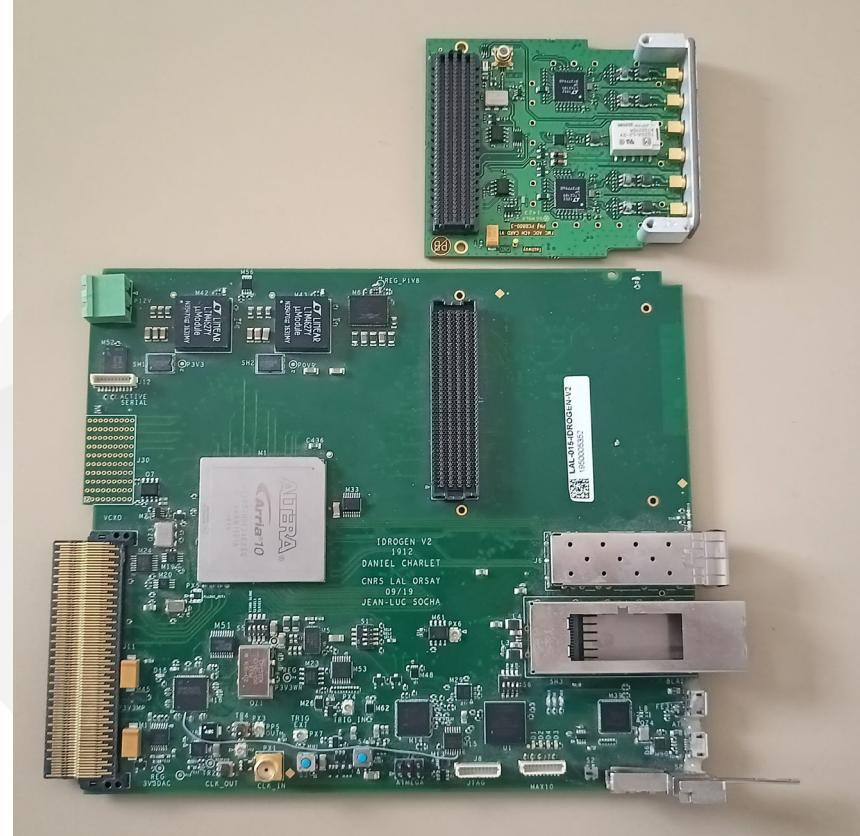

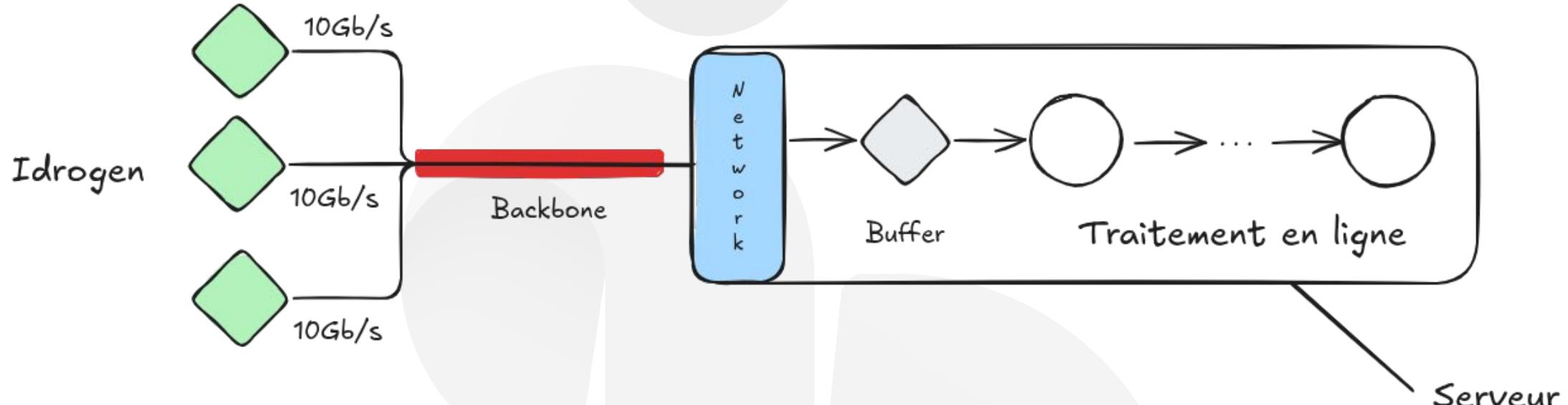

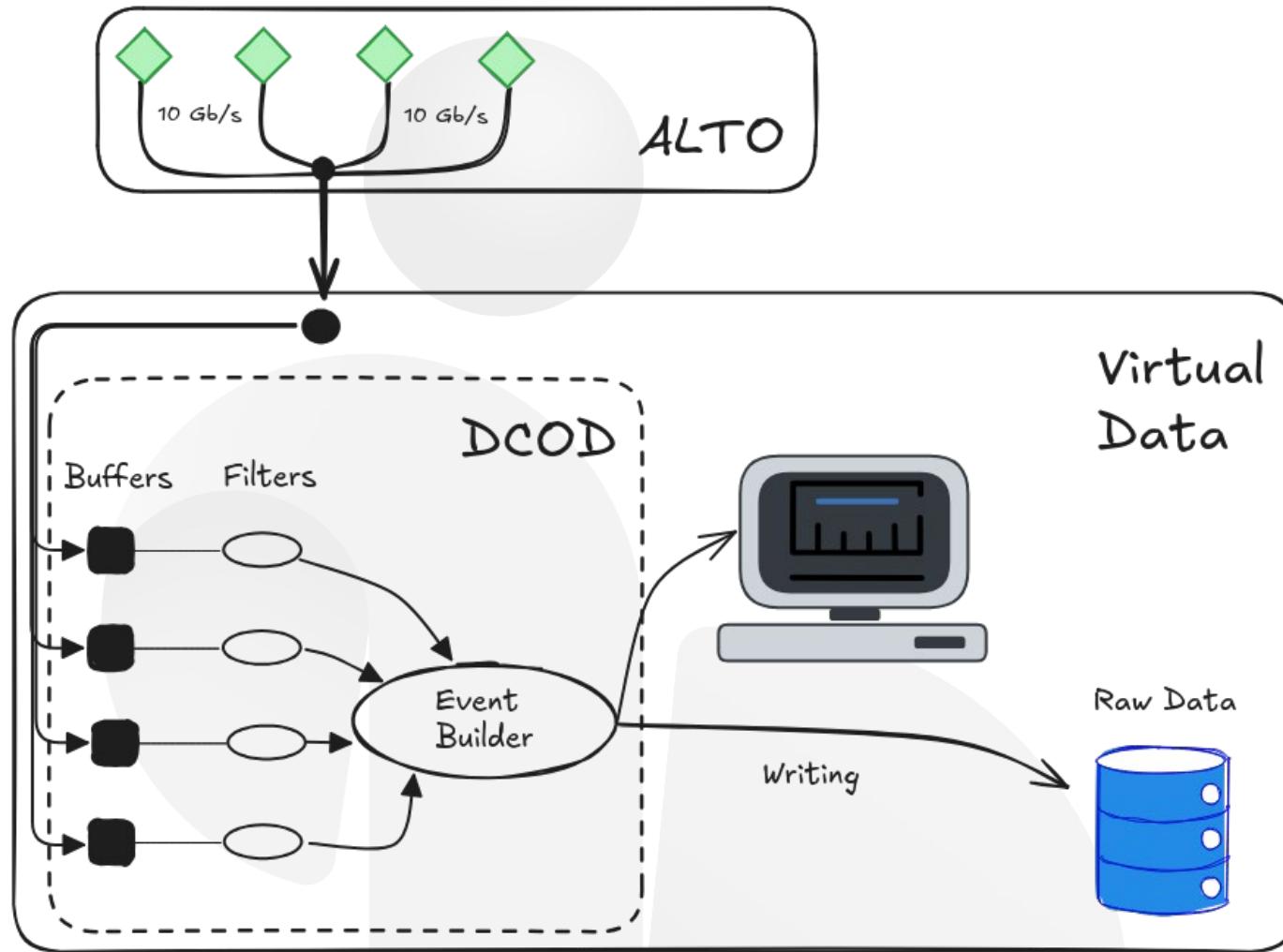

# Une Autoroute VIP pour les Particules

AG Pôle Ingénierie

04 décembre 2025

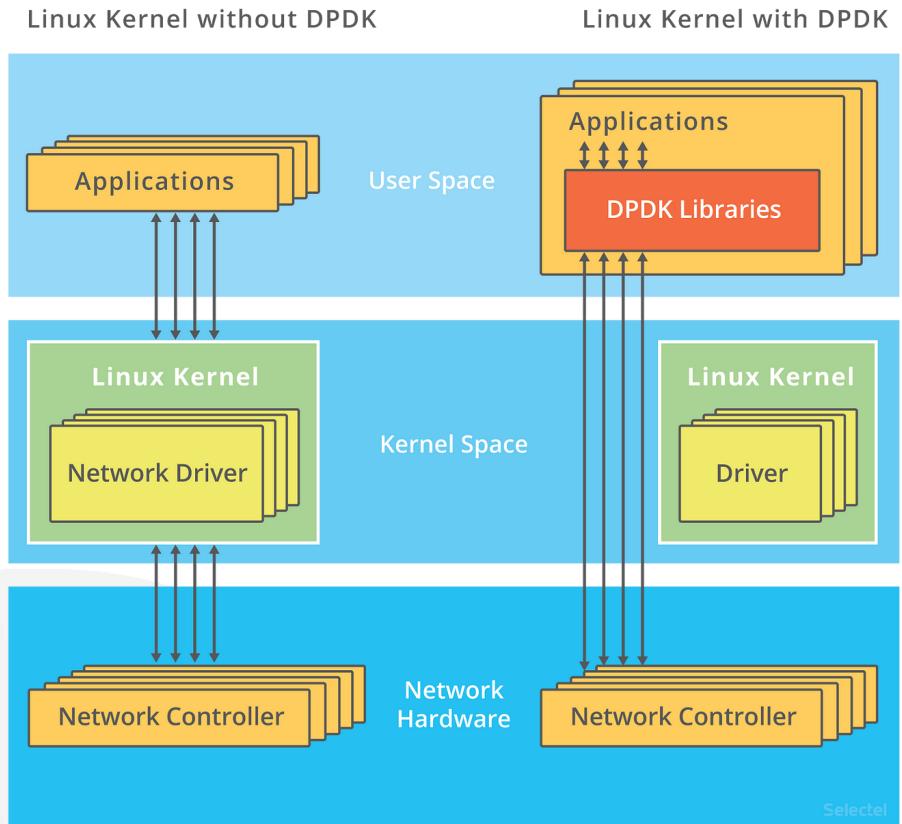

- Définition : Bibliothèque open-source (Intel)

- Objectif : Haut débit, faible latence

- Principe : Contourne la pile réseau Linux (PMD)

- Applications : Télécoms, cloud

- À IJCLab : Acquisition de données

(IDROGENE/STARE, 10 Gb/s)

Lorsque on relie une **NIC** à DPDK :

- Plus d'adresse IP

- Protocoles standards indisponible

- **Résultat** : la carte devient un fantôme sur le réseau

Laboratoire de Physique

des 2 Infinis

Pour contourner ce problème, la carte doit s'identifier spontanément sur le réseau :

- Envoyer un GARP toutes les 3 minutes

- La carte est alors enregistrée dans la cache ARP des autres machines

- **Résultat :** Communication rétablie

**GARP** : Gratuitous ARP (Address Resolution Protocol)

- **Résultats obtenus :**

- 25 Gb/s sans perte de paquets

- Charge CPU considérablement réduite

- Système plus stable, interruptions éliminées

## Perspectives :

- Passage à 40 Gb/s

- Traitement des données directement sur GPU (sans copie mémoire)

- Intégration dans la chaîne d'acquisition des futures expériences

- Vers une architecture totalement parallèle et zéro-interruption

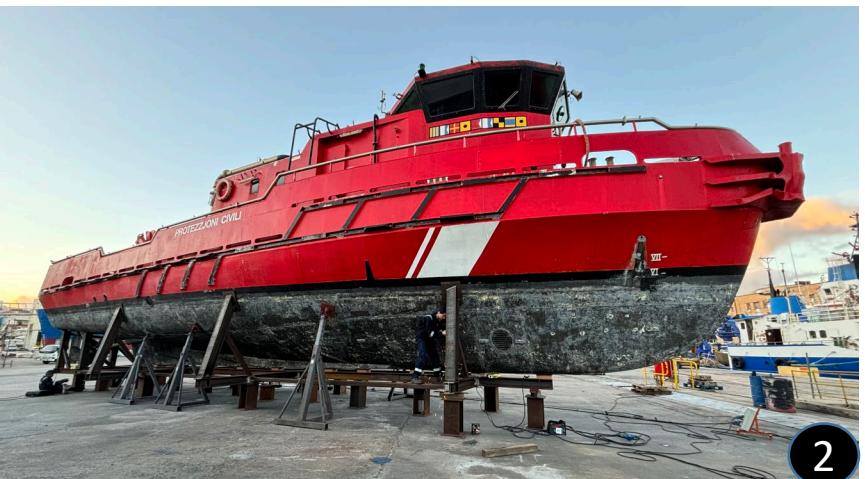

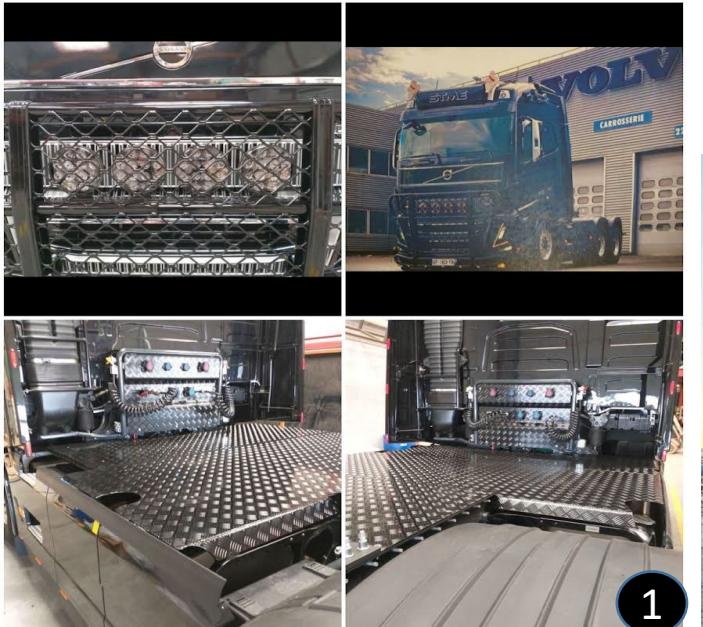

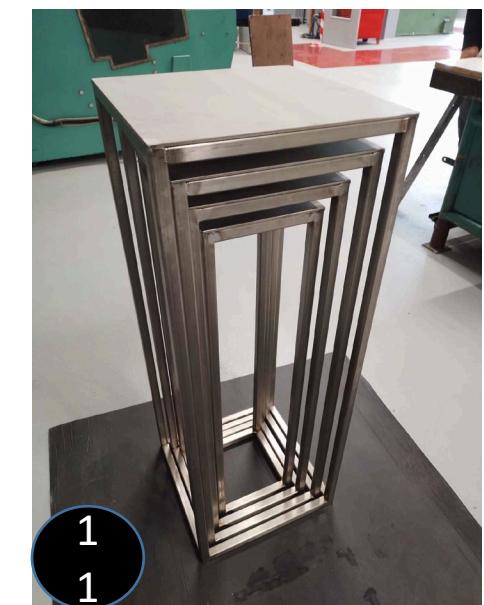

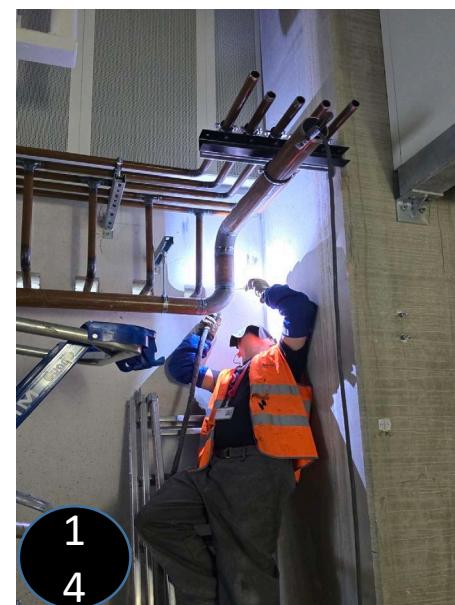

# Nathan PAYET

Dépt. Mécanique – SR2M

# Mon parcours en 180 secondes

**chaudronnier / soudeur**

**Diplômes obtenus** : - Bac de technicien en chaudronnerie industrielle

- Mention complémentaire de technicien en soudage

**Expériences** : - Transports PREMAT, 3 ans d'apprentissage en chaudronnerie (Secteur industriel)

- IJClab CNRS, 1 an d'apprentissage en soudage (Secteur de recherche scientifique)

- MMH Malta, 5 mois à l'étranger en soudage (Secteur naval)

- Siègéc, 5 mois en soudage (Secteur industriel)

- IJClab CNRS, Service mécanique → Atelier chaudronnerie / soudure

# Mes réalisations

3

7

8

9

10

11

12

13

14

- Mon activité au Laboratoire IJCLab

- Obtention du Concours des techniciens

BAP C

# Zulal KIRAZ

Dépt. Electronique

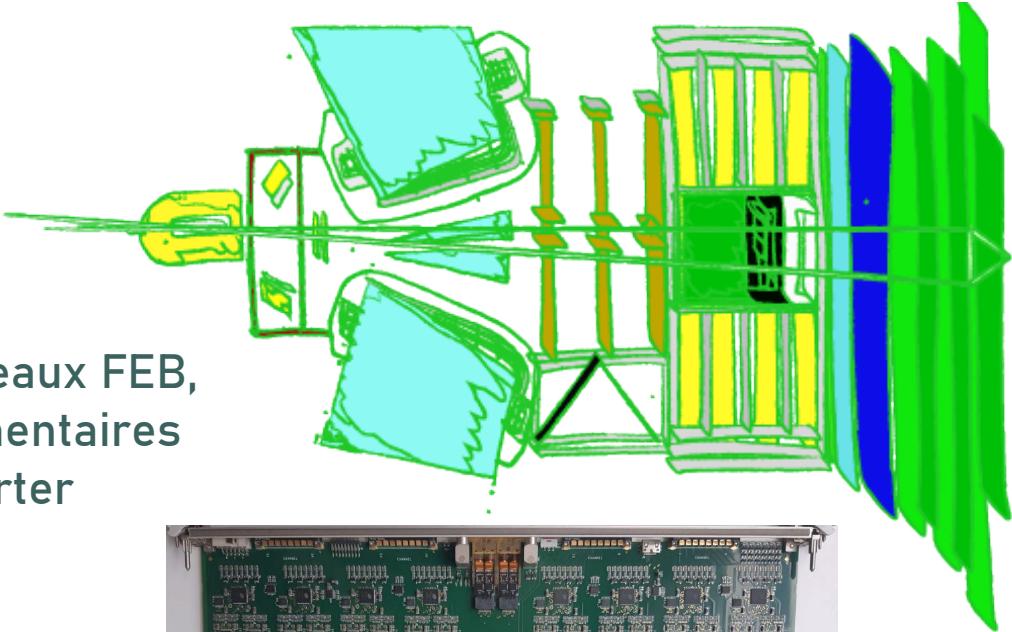

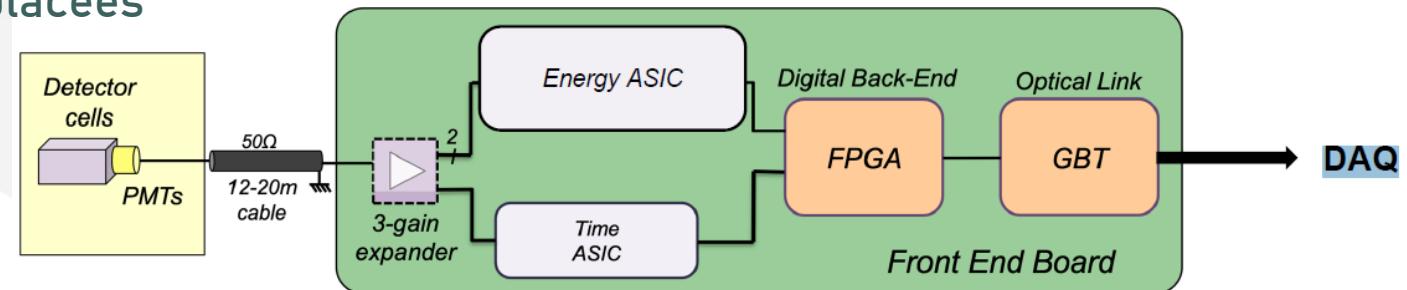

## LS3

- Une production importante de nouveaux FEB, ICECAL 3.1, 3CU et de crates supplémentaires est prévue pour le LS3 afin de supporter l'électronique mise à niveau.

- Les crates existants ont été recâblées et l'étude de marché FPGA a été finalisée.

# LS4

Toutes les cartes FE devront être remplacées pour le LS4. 32000 ch ~500 cartes

- Les cartes actuelles ne répondent pas aux exigences de radiation de U2(400 kRad à la fin du Run 5)

- Nouveau design pour intégrer à la fois les ASICs ICECAL et SPIDER

- Les alimentations devenant obsolètes → elles devront également être remplacées

Collaborations:

- CNRS / IN2P3 : LPCA (Clermont-Ferrand), IP2I (Lyon), LPC (Caen), Subatech (Nantes) – Développement du circuit SPIDER

- Instituts LHCb de Barcelone et Valence – ICECAL

- MIT & Syracuse University – Machine Learning sur FPGA

# Karim HASNAOUI

**Dépt. Informatique - Développement**

# HPC : travailler à l'échelle d'un supercalculateur

## HPC et supercalculateur

- HPC signifie **High Performance Computing**, en français **Calcul Haute Performance**.

- Il s'agit d'utiliser un **supercalculateur** pour faire le plus rapidement possible une grande quantité de calculs.

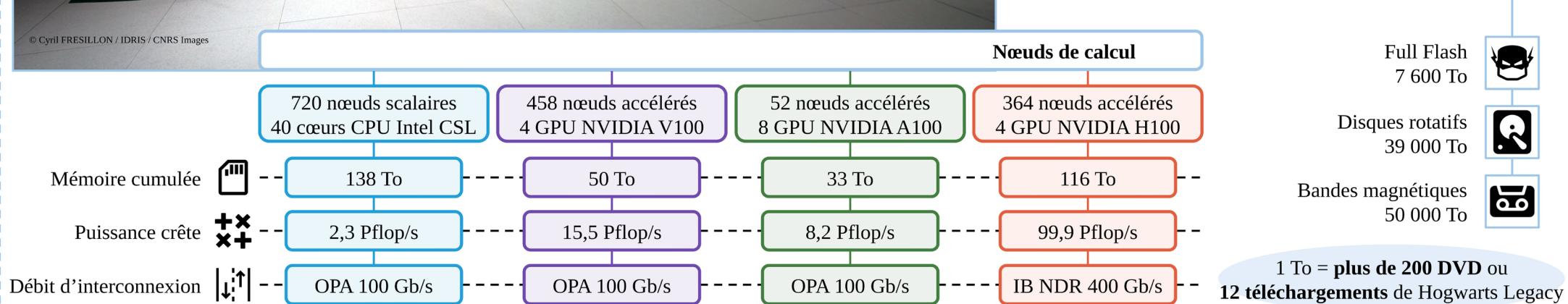

- Un supercalculateur peut être vu comme **l'assemblage de plusieurs milliers d'ordinateurs** reliés entre eux par un **réseau d'interconnexion à très haut débit**.

- On parle de **nœuds de calcul** interconnectés.

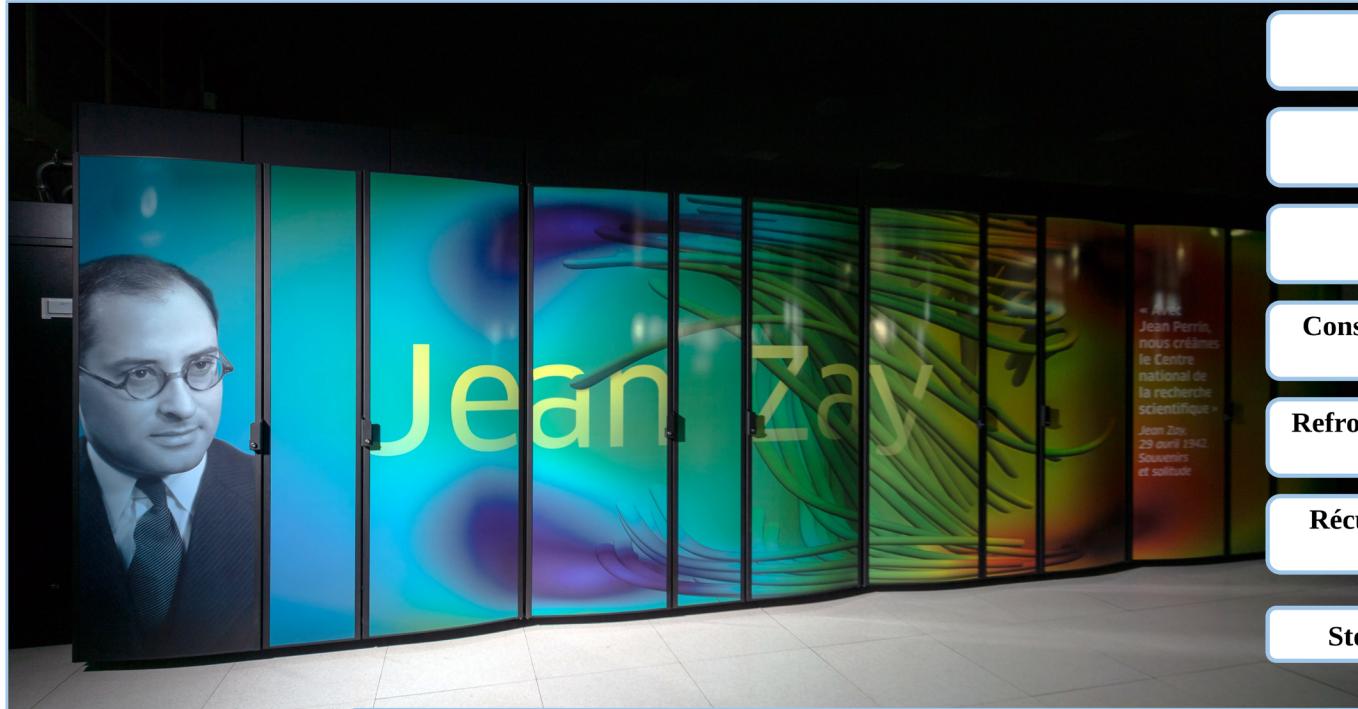

- **Jean Zay** est le supercalculateur de GENCI hébergé et exploité par le CNRS.

- **Une seconde de calcul sur Jean Zay** correspond à plus d'une journée de calcul sur un ordinateur personnel standard.

## Comment ?

- Pour faire travailler ensemble les nœuds de calcul qui composent un supercalculateur, on utilise le **parallelisme**.

- Les nœuds de calcul travaillent :

- en parallèle : chaque noeud s'occupe d'**une partie seulement du problème** ;

- de manière collaborative : les noeuds **communiquent** régulièrement entre eux pour se coordonner.

- Les communications se font par le **réseau à très haut débit** qui relie les nœuds de calcul entre eux.

- Plus il y a de nœuds de calcul, plus il est **difficile et coûteux** de les faire communiquer efficacement.

## Pourquoi faire ?

- De nombreux domaines scientifiques nécessitent de **simuler** des phénomènes naturels.

Observation

Modélisation

Simulation

- Ces simulations demandent de faire **une grande quantité de calculs** et de stocker **une grande quantité de données** en mémoire.

- Ce genre de calcul est **impossible** à effectuer sur un simple ordinateur.

- Exemples de domaines **dépendants de la simulation** :

- La prédiction de phénomènes météorologiques

- L'étude de la résistance des matériaux

- L'étude des collisions d'ions lourds

- L'entraînement d'intelligences artificielles

- La découverte de nouvelles structures moléculaires (vaccins, médicaments,...)

# Jean Zay, le supercalculateur national opéré par le CNRS

© Cyril FRESILLON / IDRIS / CNRS Images