# Sampling the signal from timing detectors for TOTEM at LHC

#### **Edoardo Bossini**

WaveCatcher and SAMPIC International Workshop Orsay, 7 February 2018

#### **OUTLINE:**

- Experiment overview

- Physics program

- Timing detectors

- Firmware for SAMPIC chip

- Future needs in HEP

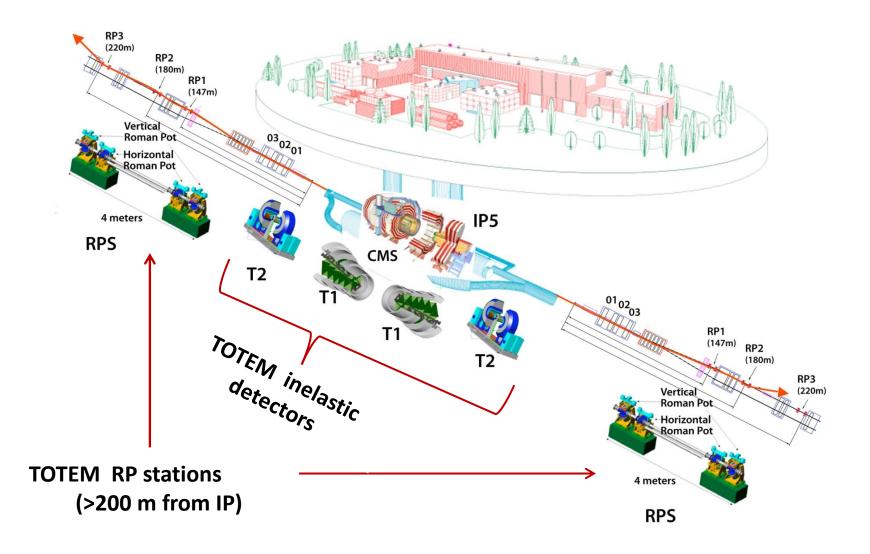

## TOTEM experiment

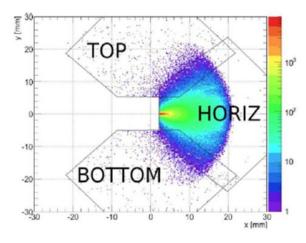

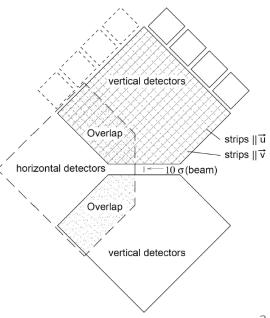

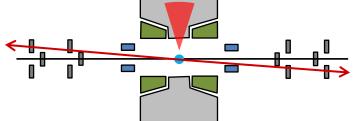

## **Roman Pots stations**

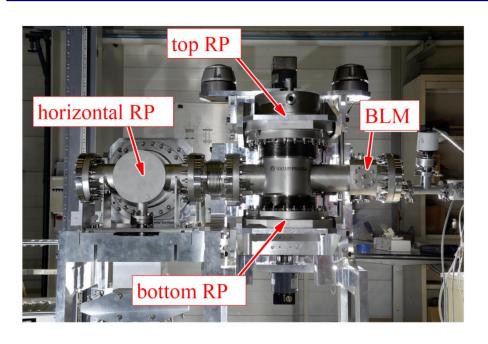

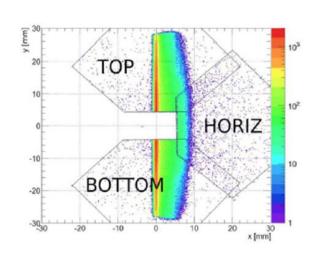

- Vacuum vessel entering the beam pipe, can be equipped with many types of detectors.

- Scattered protons with very-low |t| can be detected

- Standard units composed of 3 RP (2 vertical, 1 horizontal)

Distance from IP5 200-220 m

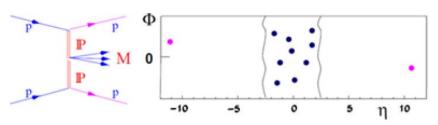

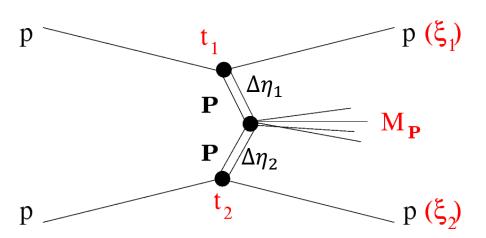

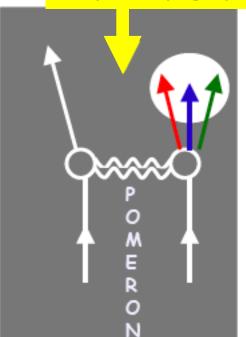

## Central Exclusive Production

CMS and TOTEM works together to performs CEP studies. trigger information are exchanged and data can be offline merged.

ightharpoonup Comparison/prediction from forward (TOTEM) to central (CMS) system:  $M_{PP}$ ,  $p_{T,z}$ , vertex

With CMS data central exclusive production can be investigated with strong BG rejection

For CEP studies in standard LHC condition the CT-PPS detector (based on TOTEM RP system) has been developed, fully integrated in CMS

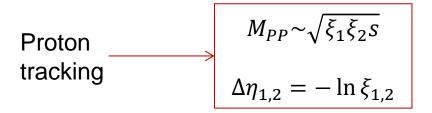

# **TOTEM-CMS** Physics program

Unprecedent low- $\xi \rightarrow$  almost pure gluon-gluon production

LHC as a gluon-gluon collider

selection rules for system X: J<sup>PC</sup> = 0<sup>++</sup>, 2<sup>++</sup>

- $\triangleright$  Glueball searches ( $f_0$  tensorial states)

- > Low mass resonances/meson pair  $(\pi\pi, KK, \rho\rho, \eta\eta)$ :

- Spin

- Decay modes

- Branching ratios

- $\triangleright$  Exclusive  $c\bar{c}$  states production  $(\chi_c)$  with different states resolved

- $\blacktriangleright$  Exclusive  $J/\psi$  and  $(\psi_{2s})$  production:

- Direct DDIS HERA confrontation

$J_z$ = 0 selection rule  $\Rightarrow$  pure gluon jets

- Cross-sections extremely sensitive to important & subtle QCD effects:

- generalized gluon PDFs

- rapidity gap survival probabilities

- "Sudakov" factors.

#### BSM search:

- Missing mass/momentum

- Rapidity gap violation

# Timing detectors

Higher the LHC luminosity, higher the probability to have more than one simultaneous pp interaction (with mean  $\mu$ )

Reconstruction of primary vertex of detected protons with TOTEM Roman Pots (RPs) limited  $\rightarrow$  difficult if  $\mu>0.1$

Max luminosity mandatory to access low crosssections ( $\mu$ ~1 for 90 m run, much higher in standard runs) Measure of the proton time of flight in the two arms:

$$> Z_{PP} = c\Delta t/2$$

With few tens of ps resolution (for MIP)

Diamond[1] and UFSD[2] detectors developed.

Both technologies actually used in the RP

ZZd i

#### Readout

Both technologies have similar characteristics of the output signal

Rise time ~ 0.5 – 1.5 ns SNR ~ 30 – 50 Amplitude ~ 300-600 mV

Fast sampler

ToT

Discriminator +

TDC

(NINO+HPTDC)

#### Why SAMPIC:

- ✓ To achieve maximum resolution a fast sampling (5-10 Gsa/s) of the signal is mandatory.

- ✓ Low channel dead time and high input rate are also needed , even for  $\mu$ ~1.

- ✓ Low cost/channel (~200)

Used in CT-PPS due to the input rate (~ 1 MHz/channel).

Loss in performance expected to be around 30%.

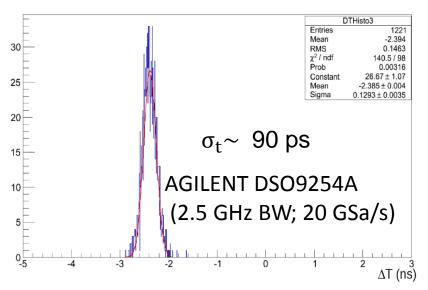

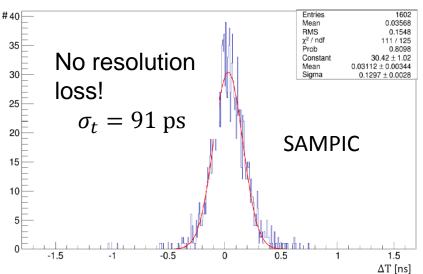

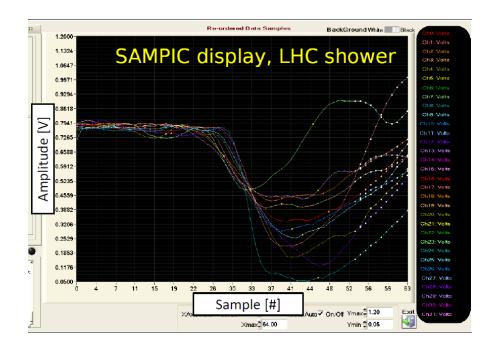

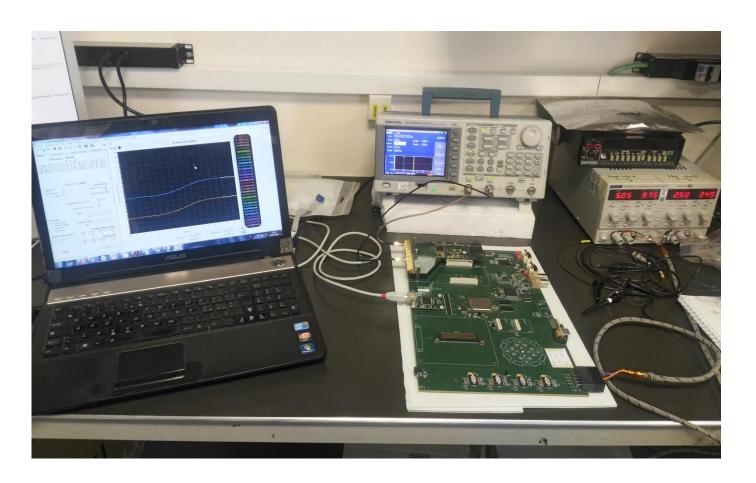

## LHC test

#### Tested in the LHC tunnel in 2015:

- sCVD diamond detector with ~90 ps intrinsic resolution[3] (sensor + amplifier)

- Standard module from LAL

- 6.4 GSa/s with 11 bit ADC resolution

- No loss of resolution compared to oscilloscope!

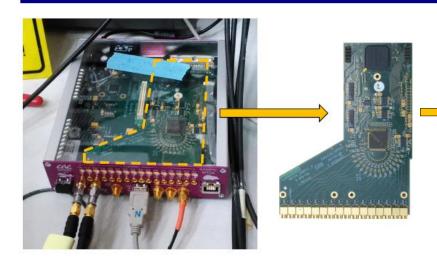

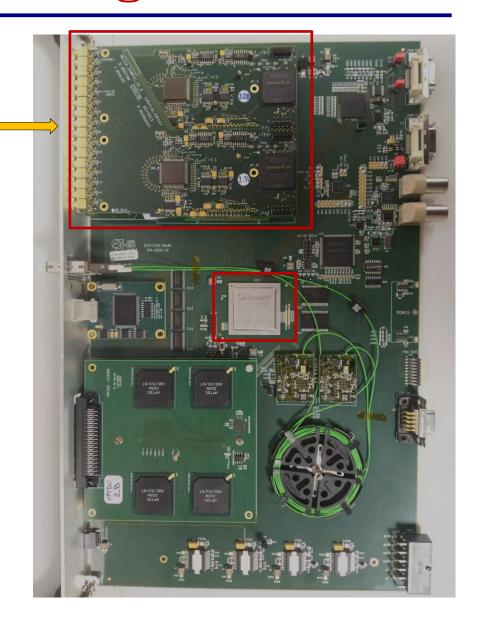

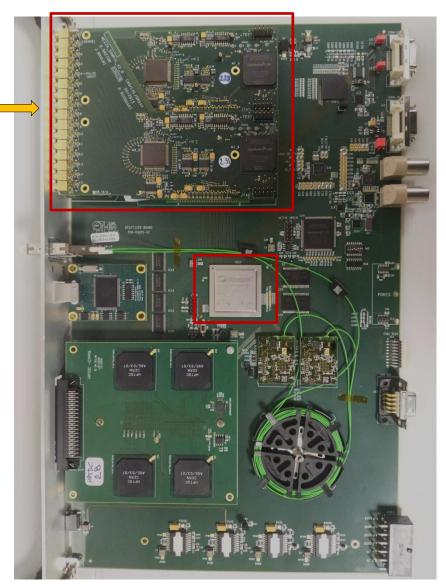

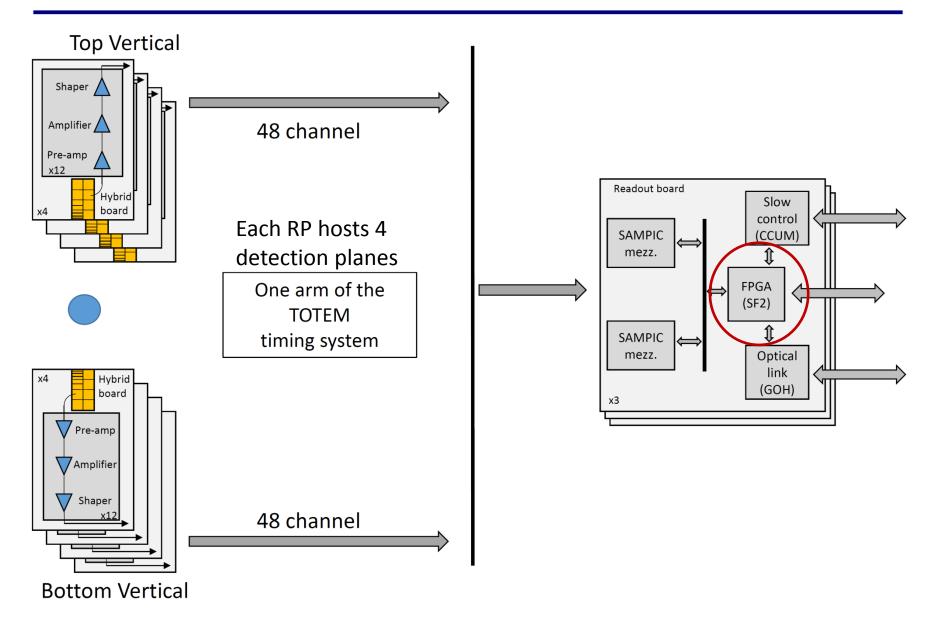

# Mezzanine integration

Special needs for the SAMPIC for real data taking:

- ➤ Chip configuration with I<sup>2</sup>C

- Readout with optical link (GOL chip)

- Compatibility with the high precision clock distribution

- USB interface for debugging and testbeam

Digitizer board

# Mezzanine integration

Digitizer board developed to integrate SAMPIC or HPTDC mezzanine in TOTEM/CMS environment.

All functionality are handled by the a radiation tolerant FPGA (Microsemi Smartfusion M2S150)

More details in G.Antchev talk!

# TOTEM TOF system

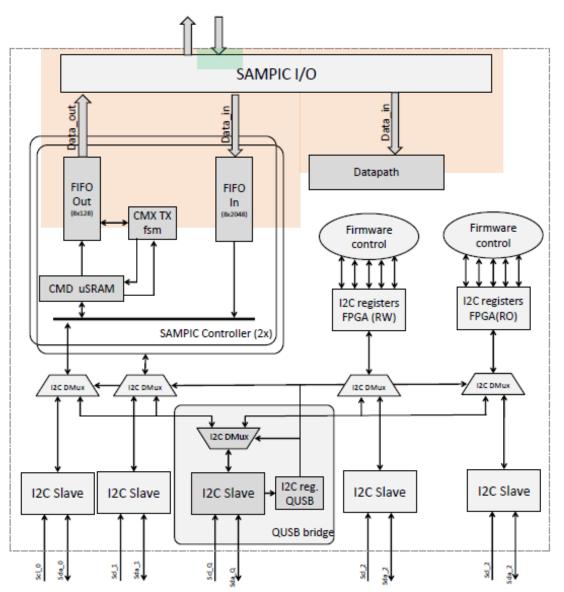

# Control firmware

- 4 slave I2C:

- FPGA register

- 2xSAMPIC config

- 1 QUSB

- Control system shared by QUSB and TOTEM control system to allow maximum testability

- Firmware builds LPBUS data packet compatible with SAMPIC mezzanine

- Check of SAMPIC configuration packet available

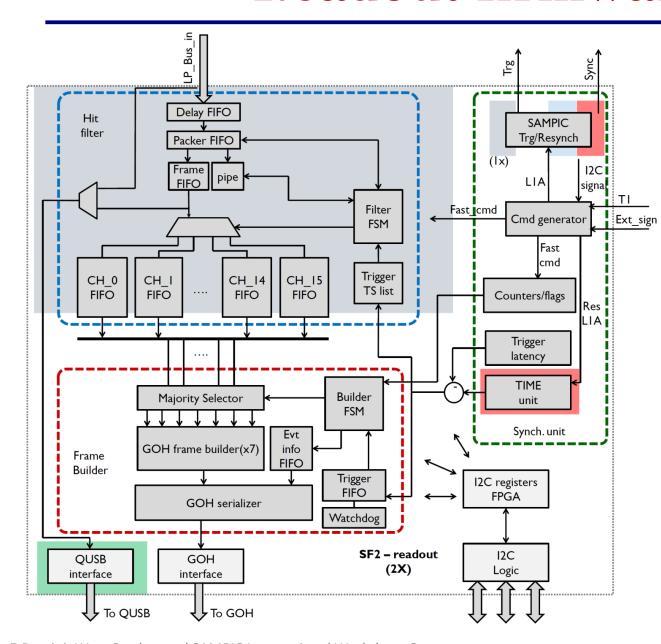

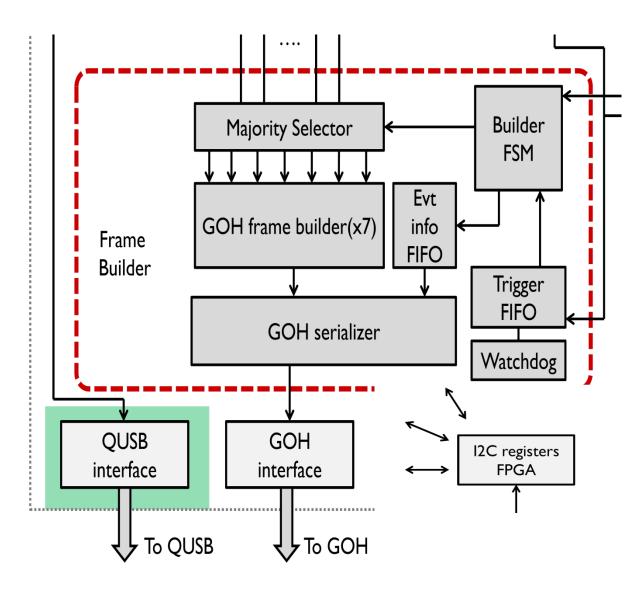

## Readout firmware

Trigger latency ~ 6 us

1 Frame for each trigger

No frame if no trigger

Max frame size ~ 350 B

Trigger rate up to 100kHz

Hit selection, frame building and data reduction to be done inside Digitizer central FPGA (Microsemi SF2)

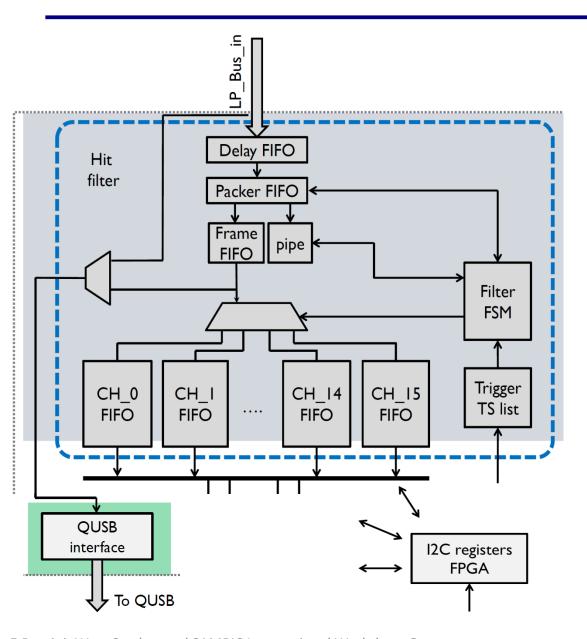

## SAMPIC hit filter

#### Frame Filter

- Delay of incoming frames

- Check frame integrity (header, trailer, WC)

- Timestamp reconstruction and matching with trigger list

- Event rejected or send to channel FIFO

- USB readout available

# DAQ frame builder

#### Event builder

- Selection of up to 7 matching channels

- Event built after ~100 us from trigger arrival to collect all frames

- Assembly of global event info

- Data reduction (factor ~ 0.5)

- Serialization of the event stream

- GOH output (16 bit data bus)

#### Actual SAMPIC configuration:

7.8 Gsa/s @ 8 bit resolution 24 samples

# Project status

- > Full system under test in Lab.

- > All board functionalities successfully tested. Readout chain fully working.

- > Expected to be installed in the tunnel in 4 weeks from now

## Future needs in HEP

Even more challenging for LHC phase II with expected rates up to <u>3/4 MHz</u> for each channel:

- Present Sampic bottleneck (Self-triggering mode needed) in data transfer out from the chip. Can be improved by integrating the SAMPIC chip in the motherboard, allowing to profit of the 12 bit LVDS connection, but still not enough.

- Only a fraction of the hits must be readout (L1 trigger rate ~100KHz)

Need internal buffer to give the time from the L1 to reach back the chip (up to 6 us)

## Future needs in HEP

Even more challenging for LHC phase II with expected rates up to <u>3/4 MHz</u> for each channel:

- Present Sampic bottleneck (Self-triggering mode needed) in data transfer out from the chip. Can be improved by integrating the SAMPIC chip in the motherboard, allowing to profit of the 12 bit LVDS connection, but still not enough.

- Only a fraction of the hits must be readout (L1 trigger rate ~100KHz)

Need internal buffer to give the time from the L1 to reach back the chip (up to 6 us)

Thank you for your attention

#### References:

- [1] G.Antchev et al. (TOTEM collaboration), JINST 12 P03007 (2017)

- [2] R.Arcidiano et al., JINST 12 no.03, P03024 (2017)

- [3] M.Berretti et al. JINST 12 P03007 (2017)

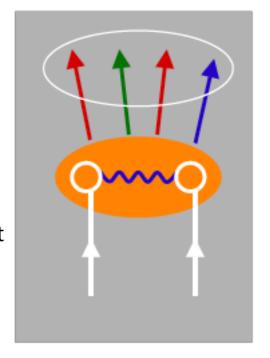

## Diffractive physics

# TOTEM

#### Non-diffractive

- Exchange of quantum numbers possible

- Rapidity gaps exponentially suppressed

$$dN/d\Delta\eta \sim e^{-\Delta\eta}$$

Incident

hadrons

acquire

color and

break apart

#### Diffractive

- No exchange of quantum number

→ no color exchange

- Rapidity gaps constant  $dN/d\Delta\eta \sim const$

## Rapidity gap

Well described by the Regge phenomenological model.

Diffraction is modeled as an exchange of one or more "objects" with vacuum quantum number, the Pomeron

One or both hadrons can survive the interaction.