# **On-Going Evolution of CMOS Pixel Sensors**

## **Joint French-Ukrainian Workshop 2021**

M.Winter / IJCLab, 28 Octobre 2021

- CONTENTS:

- Reminder:

- Specificities of CMOS Pixel Sensors

- Driving goals of their development

- Recent steps in 180 nm technology

- First results in 65 nm technology

- First results on bent sensors

- Summary & Outlook

- French involvement: 3 laboratories,  $\lesssim$  10 physicists,  $\gtrsim$  20 engineers

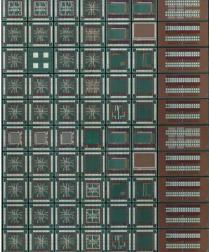

TJsc: 180 nm

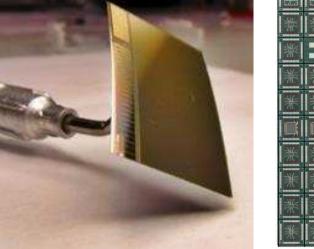

MIMOSIS-1 thinned to 60  $\mu m$

MLR-1 Reticule

# Questions Addressed with Monolithic CMOS Pixel Sensors w.r.t. Future $e^+e^-$ Colliders (and Heavy Ion Experiments)

- How well can present sensor read-out architectures be extended to future lepton collider requirements ?

- In how far are known CMOS processes optimisable for future lepton collider vertexing and tracking devices ?

- In how far can the traditionnal detector concept material budget be suppressed with more advanced concepts exploiting contemporary industrial technology ?

- In how far is the recently available 65 nm imaging process

of TJsc suited to charge particle detection and to

the ambitionned detection performance improvements

w.r.t. the limits of the known 180 nm process (granularity, power, etc.) ?

# Emblematic future vertex detector

#### **Motivation for Very Granular & Thin Sensors**

- Vertex detectors suited to future lepton colliders (e.g. Higgs-factory) & Heavy-ion experiments

- \* pixels mandatory for targetted high precision vertexing & tracking

- \* much less demanding running conditions than at LHC-pp

- $\rightarrow$  alleviated read-out speed & radiation tolerance requests

- $\Rightarrow$  privilege granularity & material budget concerns (power !)

- Generic vertexing goal:

- \* achieve high efficiency & purity flavour tagging

- → charm & tau, jet-flavour !!!

- $_{*}$  reconstruct momentum of soft tracks ( $P_t <$  100 MeV)

- \* reconstruct displaced vertex charge

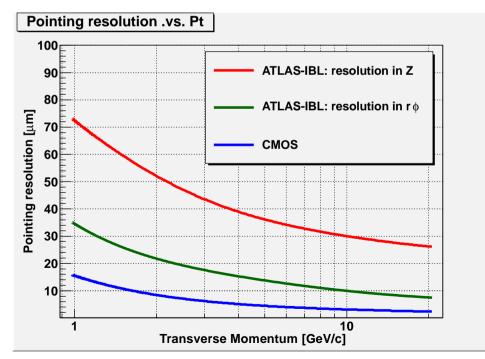

- $\rightarrow \sigma_{R\phi,Z} \leq 5 \oplus 10/p \cdot \sin^{3/2}\theta \ \mu m$  $\triangleright \ LHC: \sigma_{R\phi} \simeq 12 \oplus 70/p \cdot \sin^{3/2}\theta$

- ▷ Comparison:  $\sigma_{R\phi,Z}$  (ILD) with VXD made of ATLAS-IBL or ILD-VXD pixels

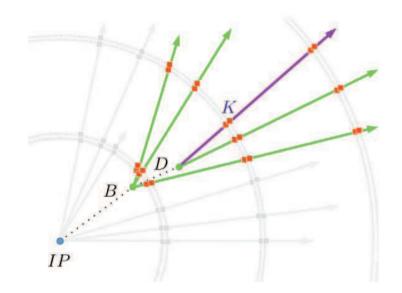

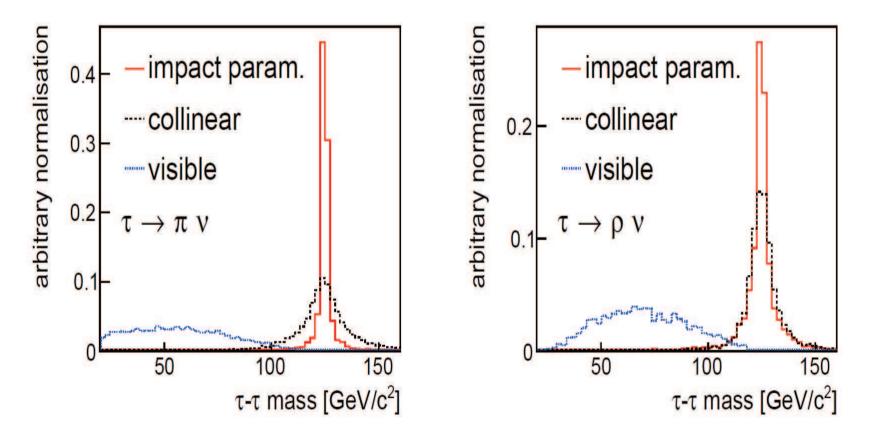

#### Impact of Vertex Detector on $\tau$ lepton reconstruction

- Impact of vertex detector on au reconstruction: example of ILD

- \* use measurements of  $\tau$  spin state in  $e^+e^- \rightarrow ZH \rightarrow \mu^+\mu^-\tau^+\tau^-$  to probe the CP nature of the Higgs boson and search for BSM manifestation by investigating CP conservation in Higgsstrahlung process and Higgs decay

- \* concentrate on hadronic decays of aus (one u only) using displaced vertex reconstruction

\* D. Jeans, Nucl. Instrum. Meth. A810, 51 (2016), arXiv:1507.01700 [hep-ex]

\* D. Jeans and G. Wilson, Phys. Rev. D 98, 013007 (2018), arXiv:1804.01241 [hep-ex]

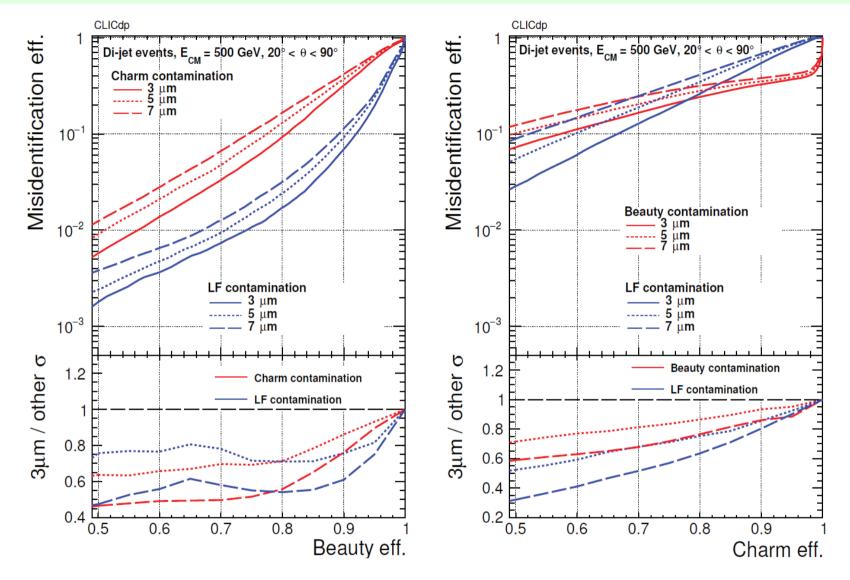

#### Impact of the Vertex Detector Spatial Resolution on b, c Tagging

fermion-pair production at E<sub>CM</sub> = 500 GeV (CLICdet vertex detector : R<sub>in</sub> = 31 mm)

D. Arominski et al., CLICdp-Note-2018-005, arXiv:1812.07337 [physics.ins-det] (2018)

•  $\sigma_{sp}$  = 7  $\mu m \rightarrowtail$  3  $\mu m \Rightarrow$  contaminations suppressed by  $\sim$  20% to 40% for 90% tagging efficiency

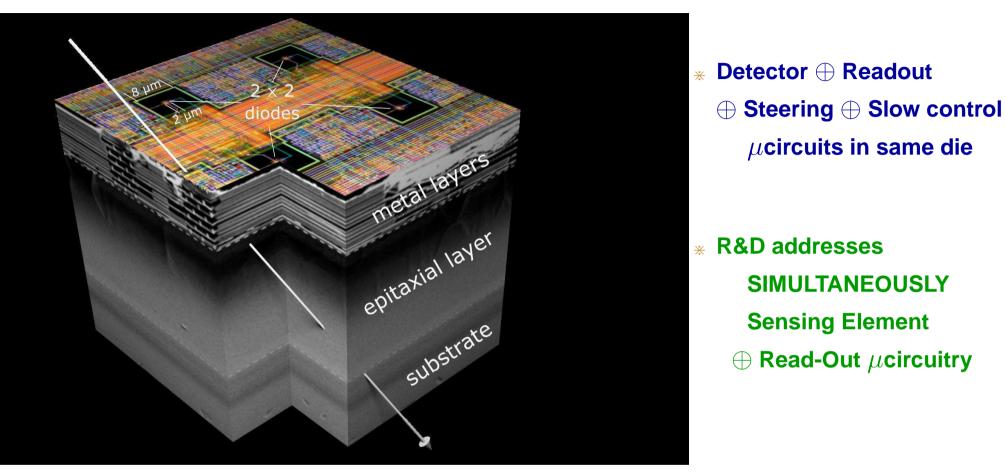

#### CMOS Pixel Sensor $\equiv$ DETECTOR with INTEGRATED FRONT-END CIRCUITRY

Cross-section of ALPIDE sensor (Courtesy of M. Mager et al.)

• Thin sensitive volume ( $\pm$  30  $\mu m$ )  $\Rightarrow$  small signal charge/pixel ( $\sim$  10<sup>2-3</sup> e<sup>-</sup>)  $\Rightarrow$  very low noise  $\mu$ circuits (< 30 e<sup>-</sup>ENC)

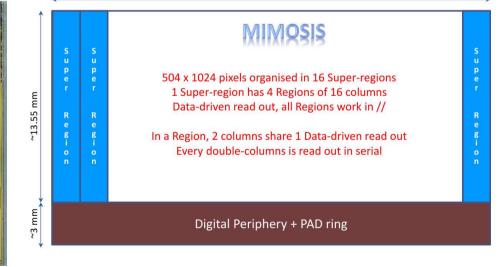

#### **Emerging Sensor in 180 nm: MIMOSIS**

# MIMOSIS development driven by the MVD of CBM/FAIR (final sensor expected in 2023) ALSO: deliverable of CREMLIN+ & forerunner for vertexing & tracking devices at future e<sup>+</sup>e<sup>-</sup> machines

- MIMOSIS pixel array derived from ALPIDE:

- $_{st}$  TJsc 180 nm imager process with high-res ( $\geq$  25  $\mu m$  thick) epitaxy

- \* modified high-res epitaxy to enhance depletion against NI radiation ( $\sim$  10 times higher than ALPIDE)

- \* 1024 col. of 504 pixels with asynchronous r.o. (ALPIDE) in-pixel discri. with binary charge encoding with DC-coupling (a la ALPIDE) & AC-coupling (new)

- \* affordable hit density  $\simeq$  50 x ALPIDE (new digital circuitry)

- \*  $\Delta t \sim$  5  $\mu s$  = twice faster than ALPIDE

- \* power density  $\gtrsim$  50 mW/cm<sup>2</sup> (vs hit density)

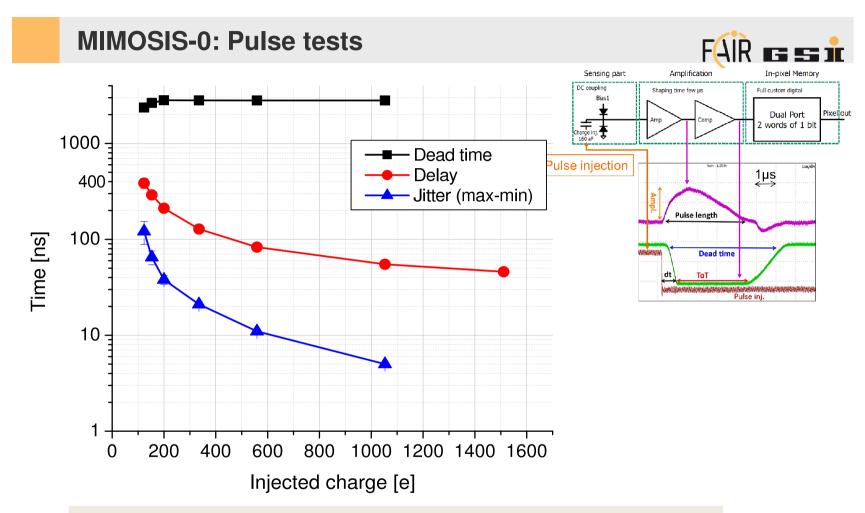

- Step-1 (2018): MIMOSIS-0 proto. (32 col. of 504 pixels)

- $_{st}$  validated in-pixel circuitry variants ( $\sim$  200 T/pixel)

- \* allowed exploring the limit of time resolution

- Step-2 (2020): MIMOSIS-1 full size proto.

- \* fabricated in 2020  $\Rightarrow$  fonctionnality tests

- \* 2021: noise & detection performance evaluation (3 beam tests)

| Physics parameter         | Requirements                                              |

|---------------------------|-----------------------------------------------------------|

| Spatial resolution        | ~ 5 um                                                    |

| Time resolution           | ~ 5 us                                                    |

| Material budget           | 0.05% X <sub>0</sub>                                      |

| Power consumption         | < 100 – 200 mW/cm <sup>2</sup>                            |

| Operation temperature     | - 40 °C to 30 °C                                          |

| Temp gradient on sensor   | < 5K                                                      |

| Radiation tol* (non-ion)  | ~ 7 x 10 <sup>13</sup> n <sub>eq</sub> /cm <sup>2</sup>   |

| Radiation tol* (ionizing) | ~ 5 MRad                                                  |

| Data flow (peak hit rate) | @ 7 x 10 <sup>5</sup> / (mm <sup>2</sup> s)<br>> 2 Gbit/s |

~30.97 mm

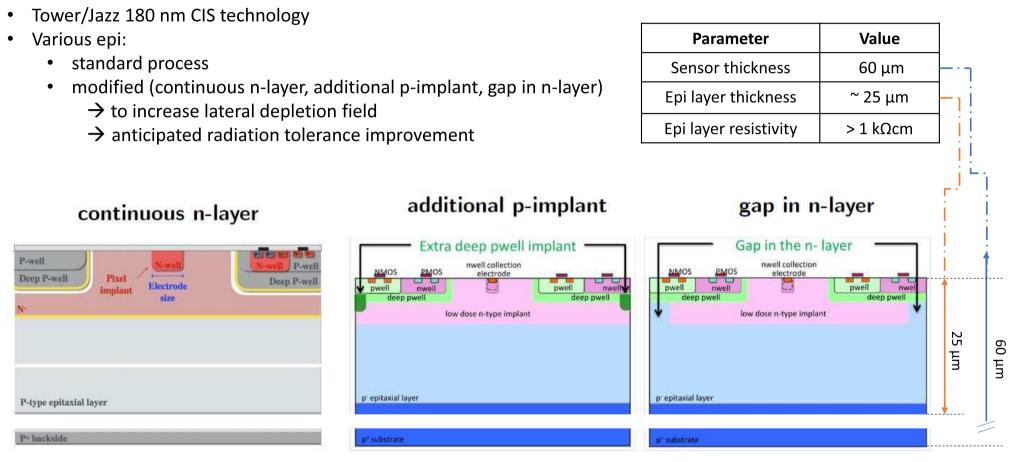

## MIMOSIS-1: EXPLORATION OF EPITAXY VARIANTS

#### **MIMOSIS-1** – TECHNOLOGY

W. Snoeys, "FASTPIX: sub-nanosecond radiation tolerant CMOS pixel sensors", ATTRACT

from R. Bugiel - TWEPP-21

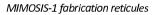

## **MIMOSIS-1: EXPLORATION OF IN-PIXEL CIRCUITRY VARIANTS**

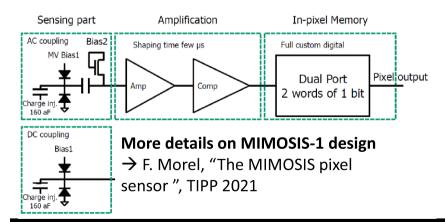

#### **MIMOSIS-1** – SENSOR OVERVIEW

- 4 submatrices •

- A, D  $\rightarrow$  optimization of CE18 for radiation hardness

- B, C  $\rightarrow$  similar to MIMOSIS-0

- Pixel size: 26.88 μm x 30.25 μm ٠

- Pixel types: ٠

- $\rightarrow$  DC pixels: ALPIDE-derived

- $\rightarrow$  AC pixels: top bias up to > 20V

- Possibility of pulse injection and pixel masking

- Matrix active area:  $\approx 4.2 \text{ cm}^2$

- Power consumption:  $40 70 \text{ mW/cm}^2 \rightarrow \text{depending on hit rate}$

from R. Bugiel - TWEPP-21

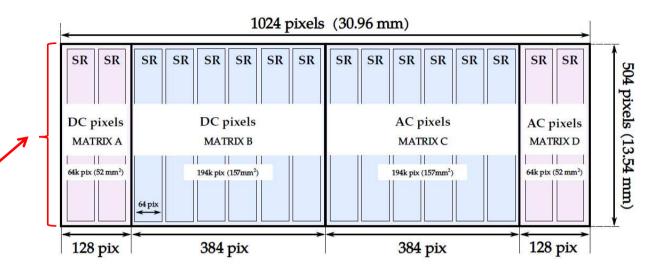

## MIMOSIS-1: NOISE PERFORMANCE

#### **GENERAL PERFORMANCE** – LABORATORY CHARACTERIZATION

#### Laboratory characterization

- characterization by pulse injection

- complex phase space of MIMOSIS1 (tuning parameters needed)

- estimation of thresholds, Fixed Pattern Noise (FPN) and Thermal Noise (TN)

- all measurements at 15°C

- Ex: performance of matrix B @ 150e threshold (before irradiation):

- TN: ~3.5 e ENC

- FPN: ~10 e ENC

Preliminary conversion factor from 1 mV  $\rightarrow$ 1 e- (within +/- 25%)

#### Summary performance before irradiation:

- Similar, satisfactory performance of all matrices

- TN: 3-5 e ENC

- FPN: 7-10 e ENC in the operation range

- AC pixels slightly lower FPN than DC

from R. Bugiel - TWEPP-21

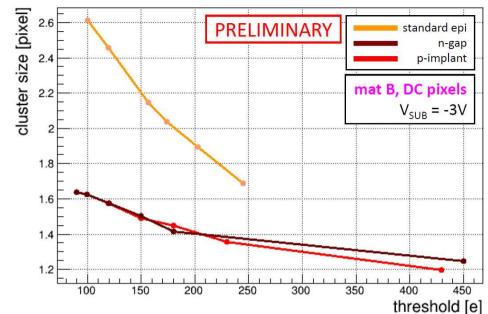

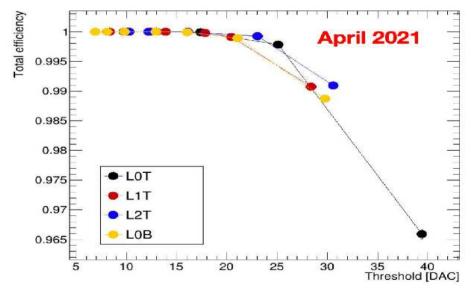

#### MIMOSIS-1: M.I.P. PREMINARY DETECTION PERFORMANCE ESTIMATES

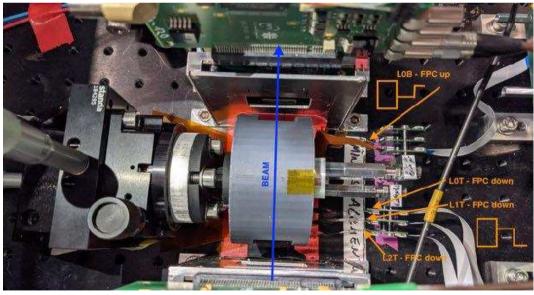

- DESY & CERN-SPS (June, Sept., Oct.):

- \* tests of 3 epitaxy variants: standard, n-gap, p-implants

- \* results still preliminary

- Cluster Size & Spatial Resolution:

- $_{*}$  cluster multiplicity has direct impact on  $\sigma_{R\phi z}$

- \* significantly smaller for modified epitaxy

- $\hookrightarrow \sigma_{st} \simeq$  5  $\mu m \rightarrowtail \sigma_{mod} \gtrsim$  6  $\mu m$

- \* cluster multiplicity still smaller with AC-coupling pixels

- $\Rightarrow$  try thicker epitaxy

- Detection Efficiency (analysis on-going)

- $*\,$  close to 100 % for all epitaxy and pixel variants over a wide range of threshold values  $\gtrsim 100~e^-$

- $_{*}$  Noisy pixel rate seems  $\lesssim 10^{-6}$

- Radiation Tolerance at  $T_{room}$  (very preliminary):

- $_{*}$  Impact of NIEL studied up to 3.10 $^{14}$  n $_{eq}$ /cm $^{2}$   $\checkmark$

- \* Impact TID studied up to 5 MRad

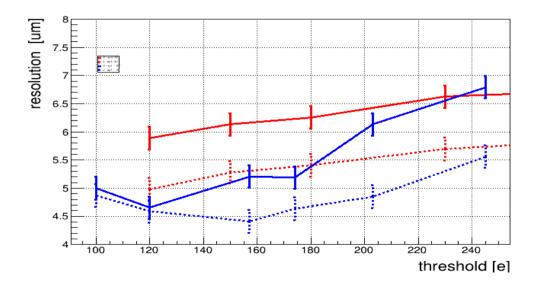

#### MIMOSIS READ-OUT SPEED POTENTIAL FOR FUTURE ELECTRON MACHINES

After optimizing trim voltages:

- Time walk + jitter <  $1\mu$ s, dead time ~ $3\mu$ s

- AC pixel (not shown) 30% slower than DC pixel

- Might reach time accuracy < 1μs (target frame readout time 5μs)

## MIMOSIS READ-OUT SPEED POTENTIAL: NEXT STEP

- New foundry submission in Octobre: MIMOSIS-0<sub>Fast</sub>

- $_{\circ}$  objective: about 10-20 times faster read-out than MIMOSIS (5  $\mu s$ )

- \* 2 flavours of in-pixel Pre-AMP: MALTA-like & IPHC

- $\hookrightarrow$  operating in the 200 ns–500 ns range

- \* minor modifications of the digital circuitry

- adaptation of DAC polarisations to the new in-pixel Pre-AMPs

- avoid MIM capacitors in DACs

- increase in-pixel current typically by factor O(10)

- $_{*}$  New EPI variants investigated (incl. 50  $\mu m$  thick)

- Status: submitted, expected back from foundry in Q1/'22

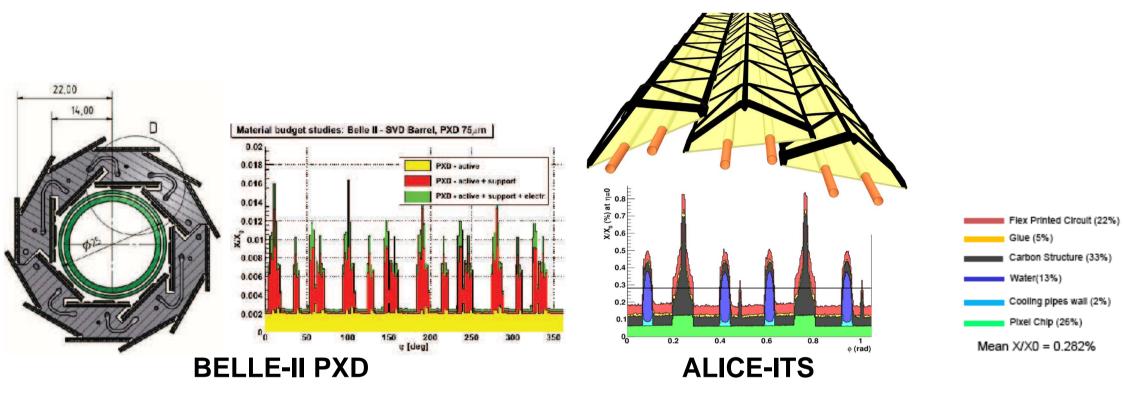

## Major R&D Goal in Coming Years: Material Budget Reduction

Physics perfo. limited by material budget of services & overlaps of neighbouring modules/ladders

- Contribution of sensors to total material budget of vertex detector layer is modest: 15 30%

- R&D objective beyond "classical" concepts:

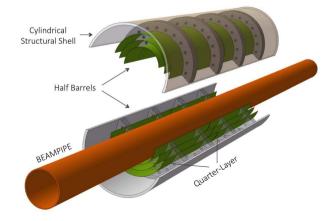

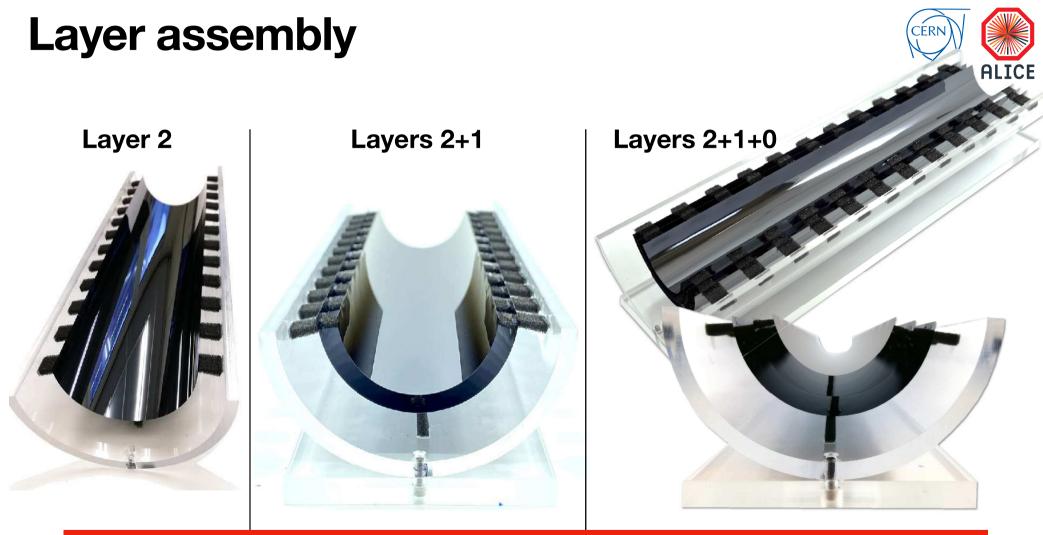

- Innermost layer: try stitched & curved CPS along goals of ALICE-ITS3, possibly with 65 nm process

- Concept with minimised mechanical support

- (e.g. using beam pipe) See Talk of M. Mager at Vertex-19, Lopud Island, Oct.'19

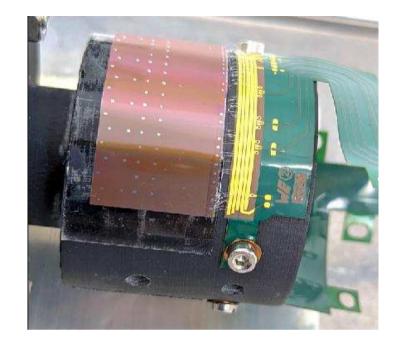

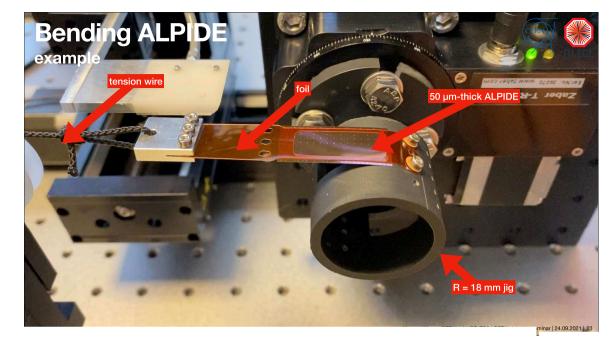

#### BENDING ACHIEVEMENTS WITH ALPIDE SENSORS

from M. Mager - CERN

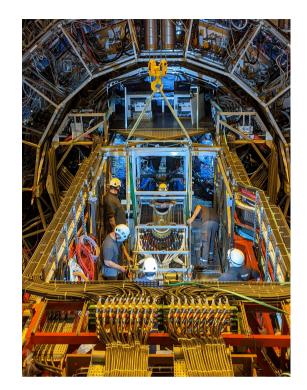

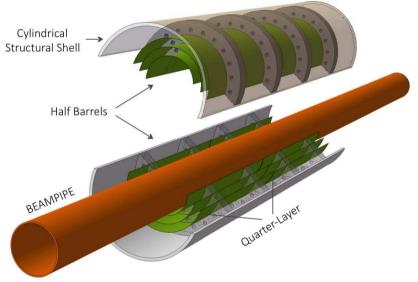

## DEVELOPING A NEW VERTEX DETECTOR CONCEPT VIA ITS-3

3-layer integration successful!

Magnus Mager (CERN) | ALICE ITS3 | CERN detector seminar | 24.09.2021 | 26

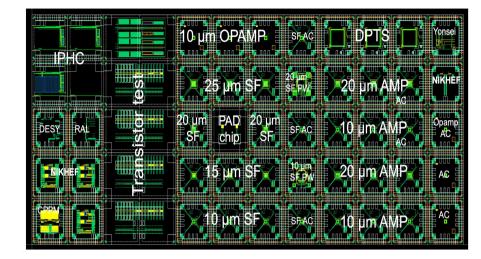

## **Exploration of a 65 nm Imaging Technology**

- Motivations of the R&D:

- \* Smaller feature size than 180 nm technology used for MIMOSIS

- $\Rightarrow$  smaller pixels, more in-pixel functionnalities, less power consumption, faster readout, ...

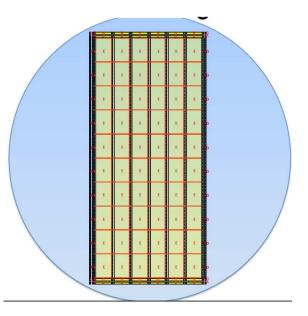

- \* Imaging technology available since  $\sim$  Spring 2020: includes stiching  $\Rightarrow$  multireticle sensors

- \* R&D coordinated at CERN (ALICE-ITS3 & EP-div)

- ITS3 goals: small pixels and very low material budget exploiting stitching for "supportless" detector layer

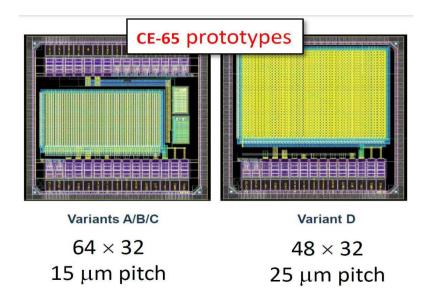

- Prototyping at IPHC for MLR1 (2020):

- Design of "elementary" test structures with CERN

- Design of 2 chips featuring arrays of 15x15 & 25x25 $\mu m^2$  pixels with rolling shutter readout & analog output

- Grouped submission (MLR1) submitted to TowerJazz

for fabrication during Winter-Spring 2020-21

- Tests just starting

## CONCLUSIONS

- MIMOSIS IN 180 NM IMAGING PROCESS:

- \* 5  $\mu m$  / 5  $\mu s$  / < 100 mW/cm  $^{2}$  / > 10  $^{14}$   ${\rm n}_{eq}/{\rm cm}^{2}$  , etc.  $\checkmark$

- $_{*}$  Added value of AC-coupling & EPI variants  $\pm$  evaluated

- \* Next steps:

- CBM-MVD: MIMOSIS-2 (Nov.'21)  $\rightarrow$  MIMOSIS-3 (2023)

- 200 500 ns variant: medium protoype submitted for fabrication Promising design for trackers adapted to future  $e^+e^-$  colliders

- **65** NM EXPLORATION:

- MLR1 chips tests starting: prelim. beam test results indicate that the process is adapted to tracking (not trivial)

- \* Next step: ER1 with stitched reticles to be fabricated in Spring '22

- \* First multi-reticle proto. foreseen in 2023 for ALICE-ITS3

- LARGE CURVED CHIPS:

- $_{*}$  Bending trials with ALPIDE (R  $\simeq$  2 cm) successful (tested on beam)

- Next steps: tests with combined sets of ALPIDE forming a plane,

& with sectors of MLR1 wafers

- Trials with 65 nm multireticule chips being prepared for ER1