# Caractérisation du circuit TEPIC : Time and Energy for Photomultipliers Integrated Circuit

De Neeff Raphaël - Service Systèmes Numériques et Acquisition / Département électronique / Pôle Ingénierie

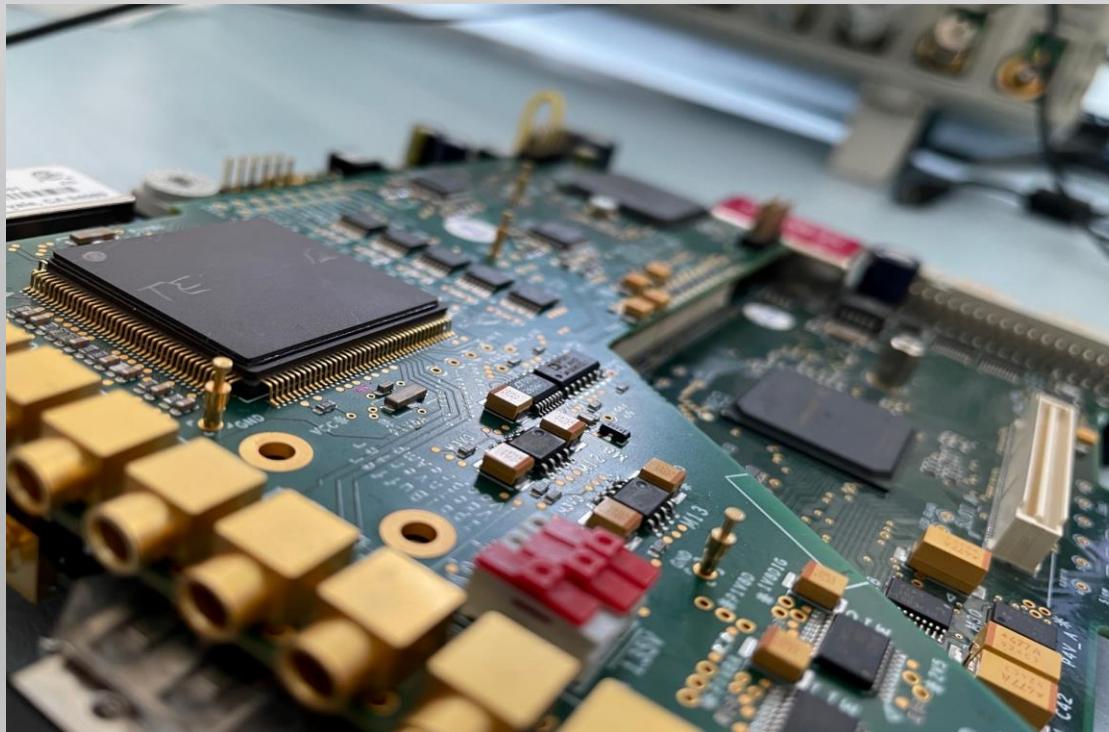

Carte électronique TEPIC.

# Sommaire

- Présentation du projet TEPIC

- Schémas de principe du circuit

- Environnement de test

- Caractérisation de la partie TDC:

- Fonctionnement du TDC de TEPIC

- Calibration

- Protocole de test

- Résultats

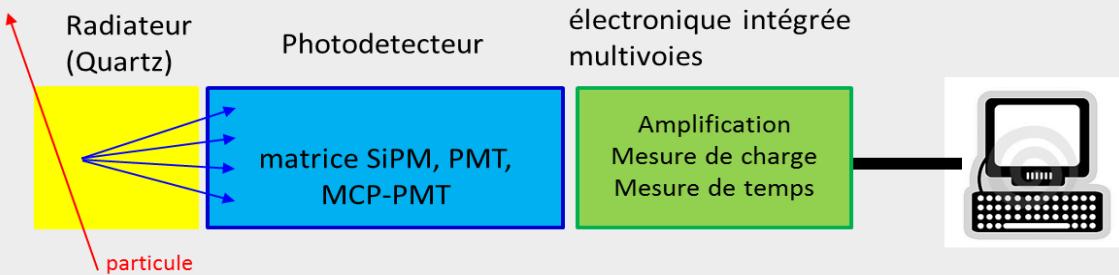

# Le projet TEPIC

- ASIC développé pour la physique des particules, projet de R&D dédié à la lecture de photodétecteurs.

- TEPIC: “Time and Energy for Photomultipliers Integrated Circuit”.

| TEPIC             |                                                   |                                                              |

|-------------------|---------------------------------------------------|--------------------------------------------------------------|

|                   | Acteurs                                           | Mesure                                                       |

| Partie analogique | IJCLab<br>Philippe Vallerand                      | Préamplification (2 options) et Shaper<br>Charge Particule   |

| Partie numérique  | LPC Caen<br>Laurent Leterrier<br>Sebastien Drouet | Time to digital converter (TDC)<br>Temps d'arrivée particule |

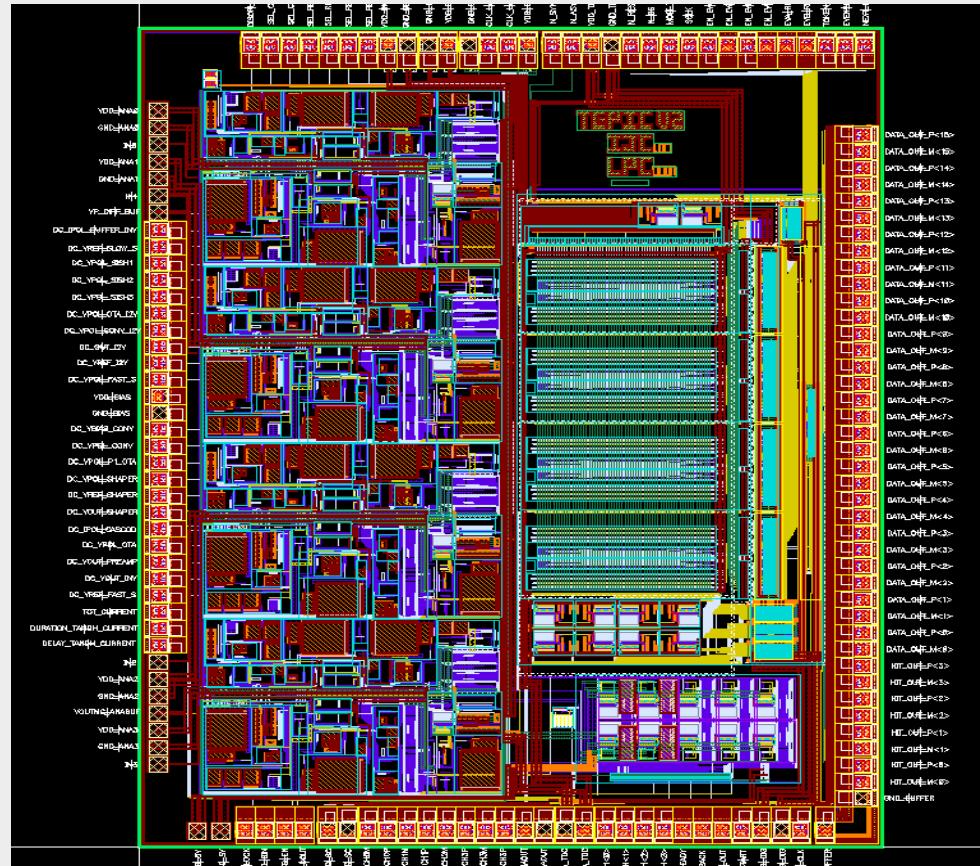

- Nombres de voies : 4

- Surface = 10 mm<sup>2</sup>

- Technologie TSI 180 nm

- Boîtier céramique QFP 160 broches 28 mm x 28 mm

- Ligne de financement: Projet Fracas (domaine médical, arrêté) et Cherenkov Lab (projet IN2P3)

Layout de la puce TEPIC.

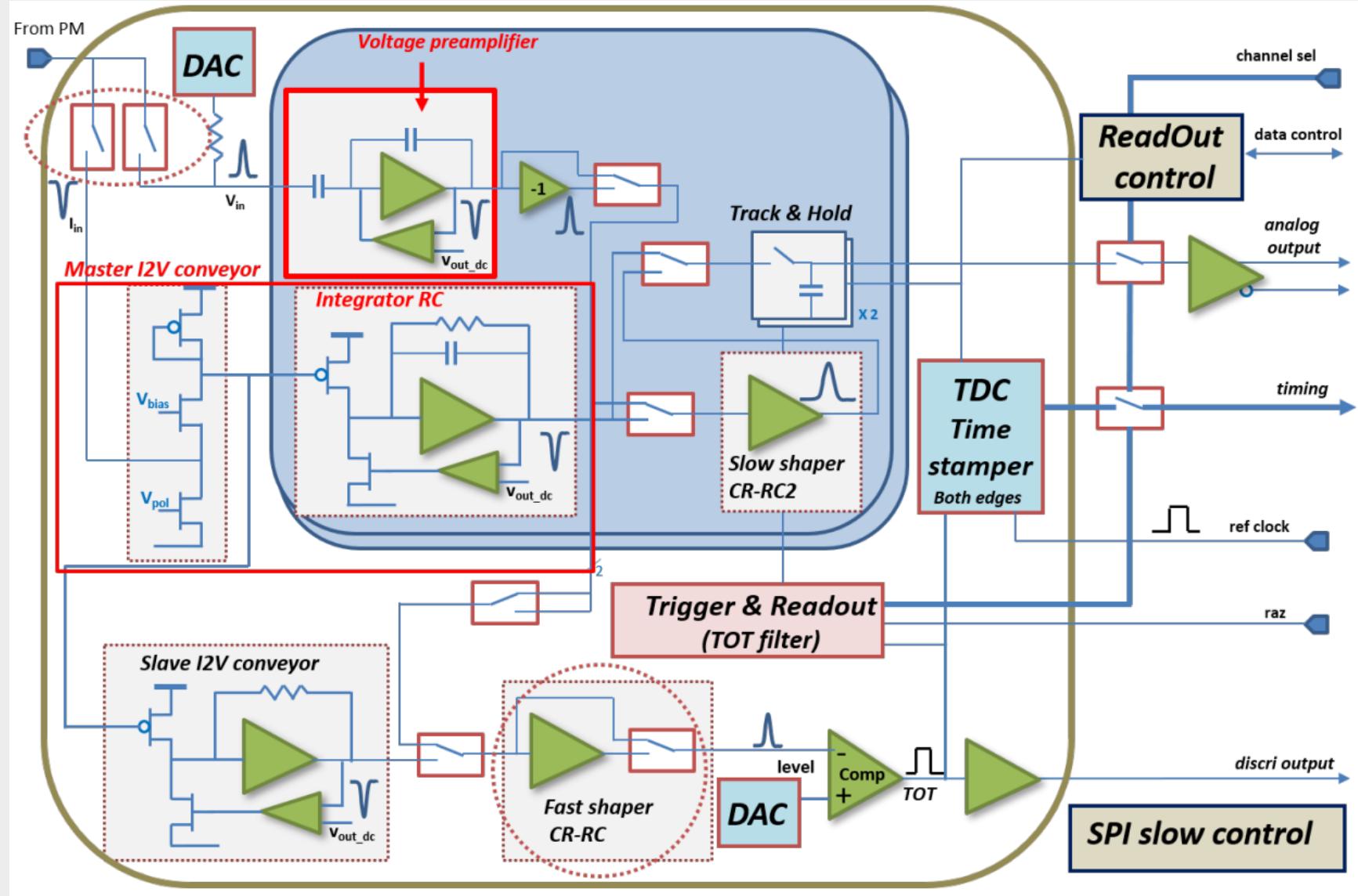

# Schéma de principe du TEPIC: détail partie analogique

➤ Schéma pour une voie (4 en tout)

- La partie amplification en tension à base d'amplificateur cascode.

- La partie amplification en courant, composée du convoyeur de courant à base de transistors MOS et de l'intégrateur RC.

Schéma de principe de la puce TEPIC, d'après P. Vallerand.

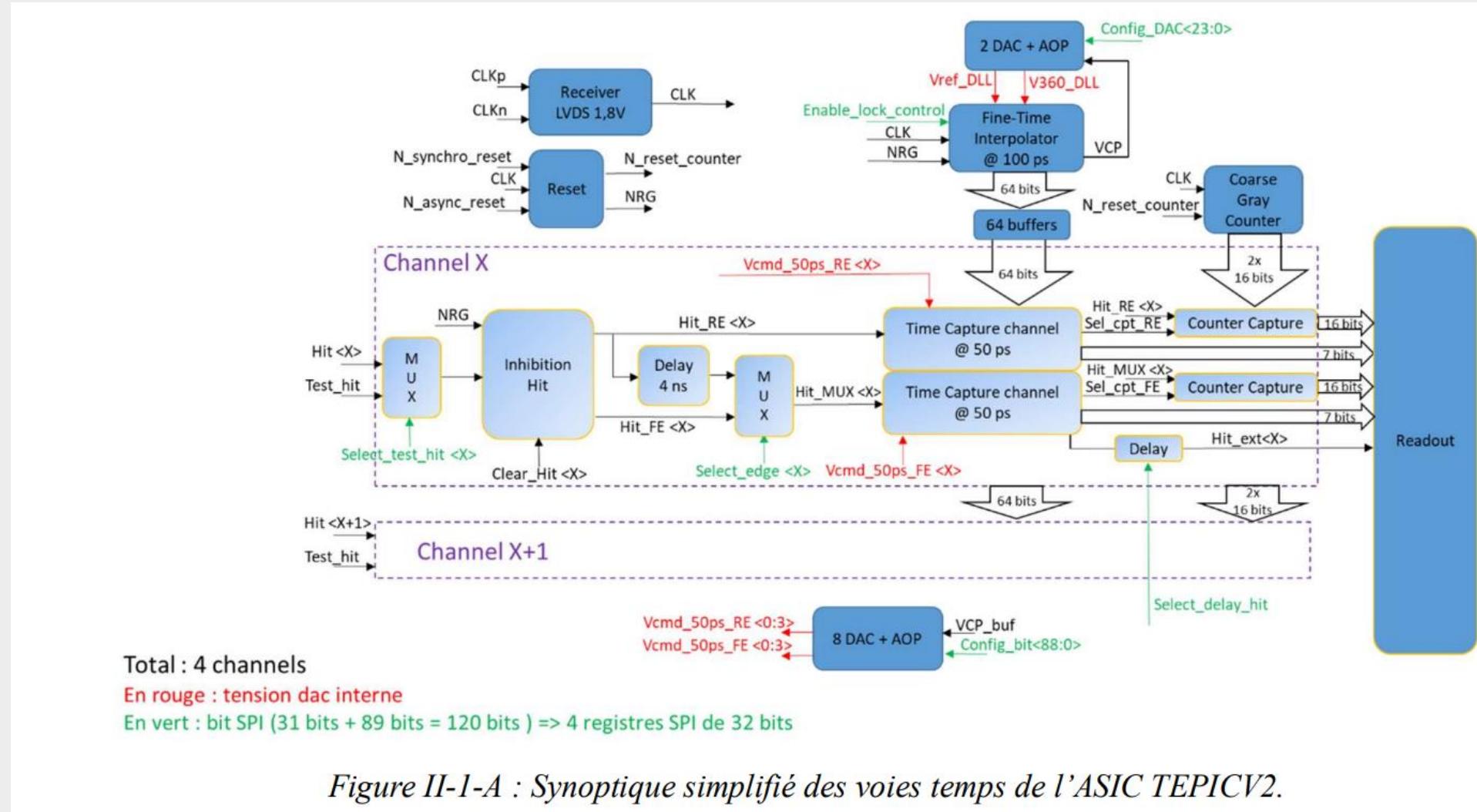

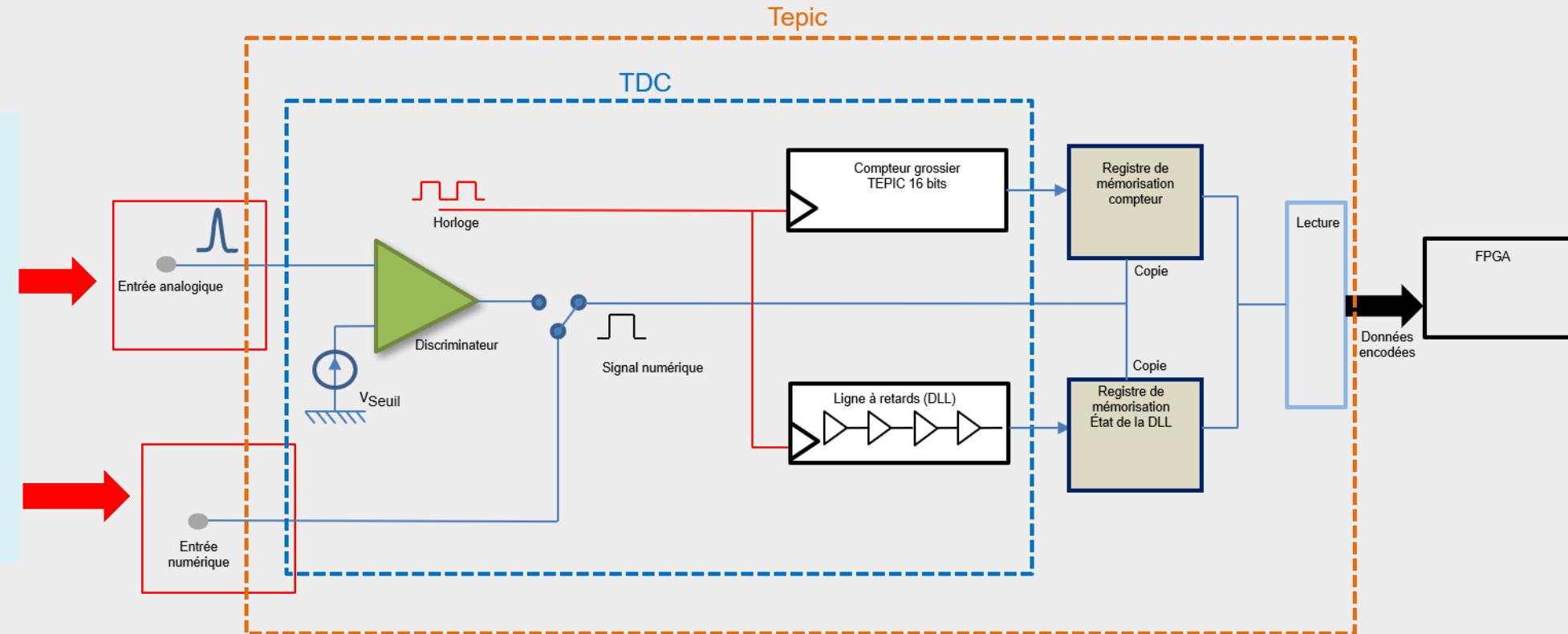

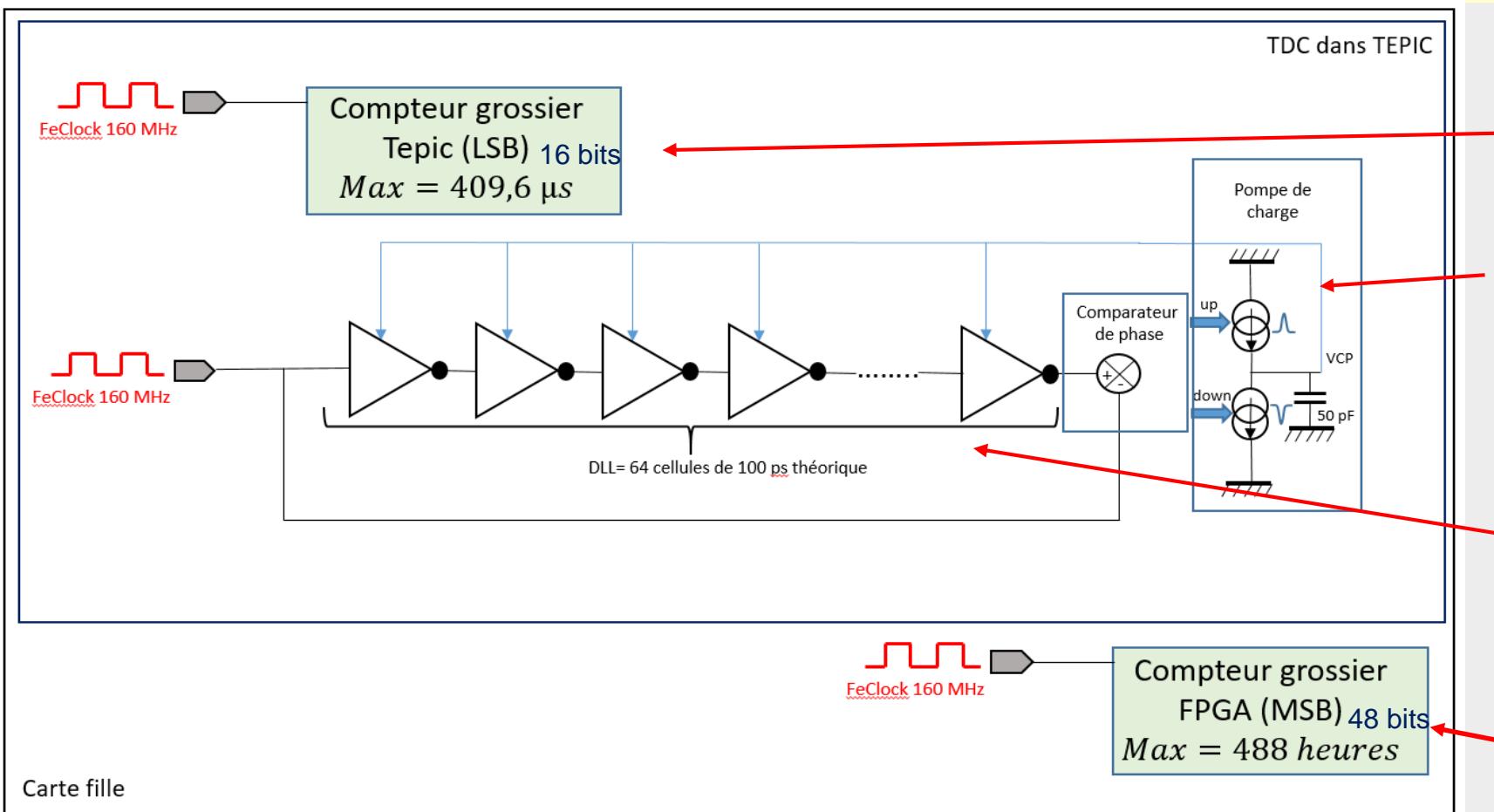

# Synoptique de la partie mesure de temps: TDC

*Synoptique de la voie temps du TEPIC, L. Leterrier.*

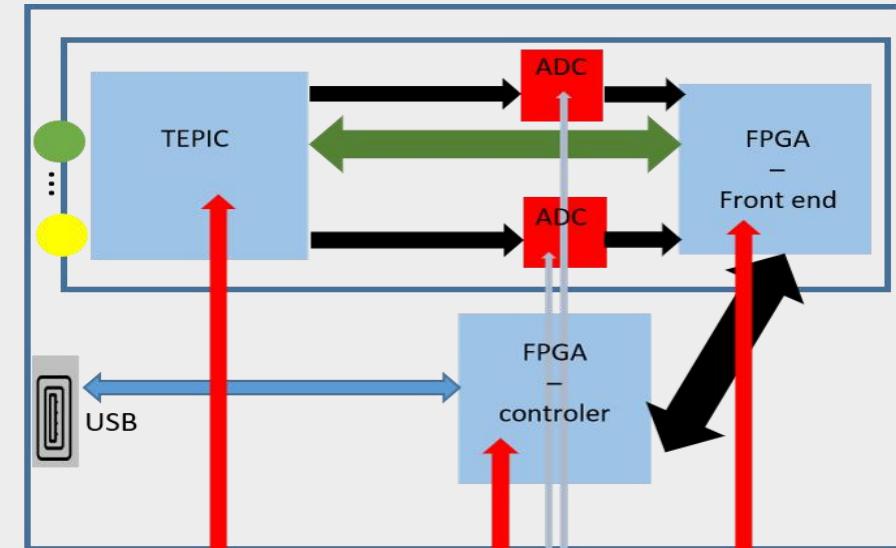

# Environnement de Test de l'ASIC TEPIC

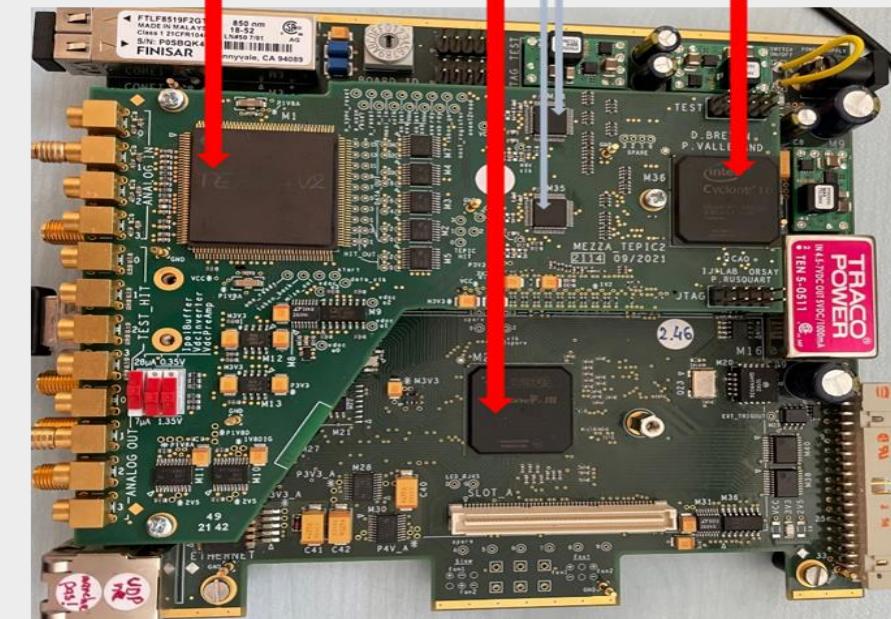

- **Carte Mezzanine** conçue par D. Breton en collaboration avec Ph.Vallerand.

- Carte compatible avec les cartes mères (**MezzaMother**) utilisées dans d'autres projets ( WaveCatcher, Sampic, ILC ...)

- Accès par USB et librairie **LALUsbML** (Chafik Cheikali).

- CAO (Routage) : P.Rusquart

- Câblage de la carte à IJCLab par le **Service CAO Prototypage et Réalisation**: J.Favre et B.Debennerot

- Firmware : J.Maalmi

- **Logiciel de contrôle et acquisition** : R. De Neeff avec l'aide de J.Maalmi

Carte mezzanine TEPIC sur carte mère MezzaMother.

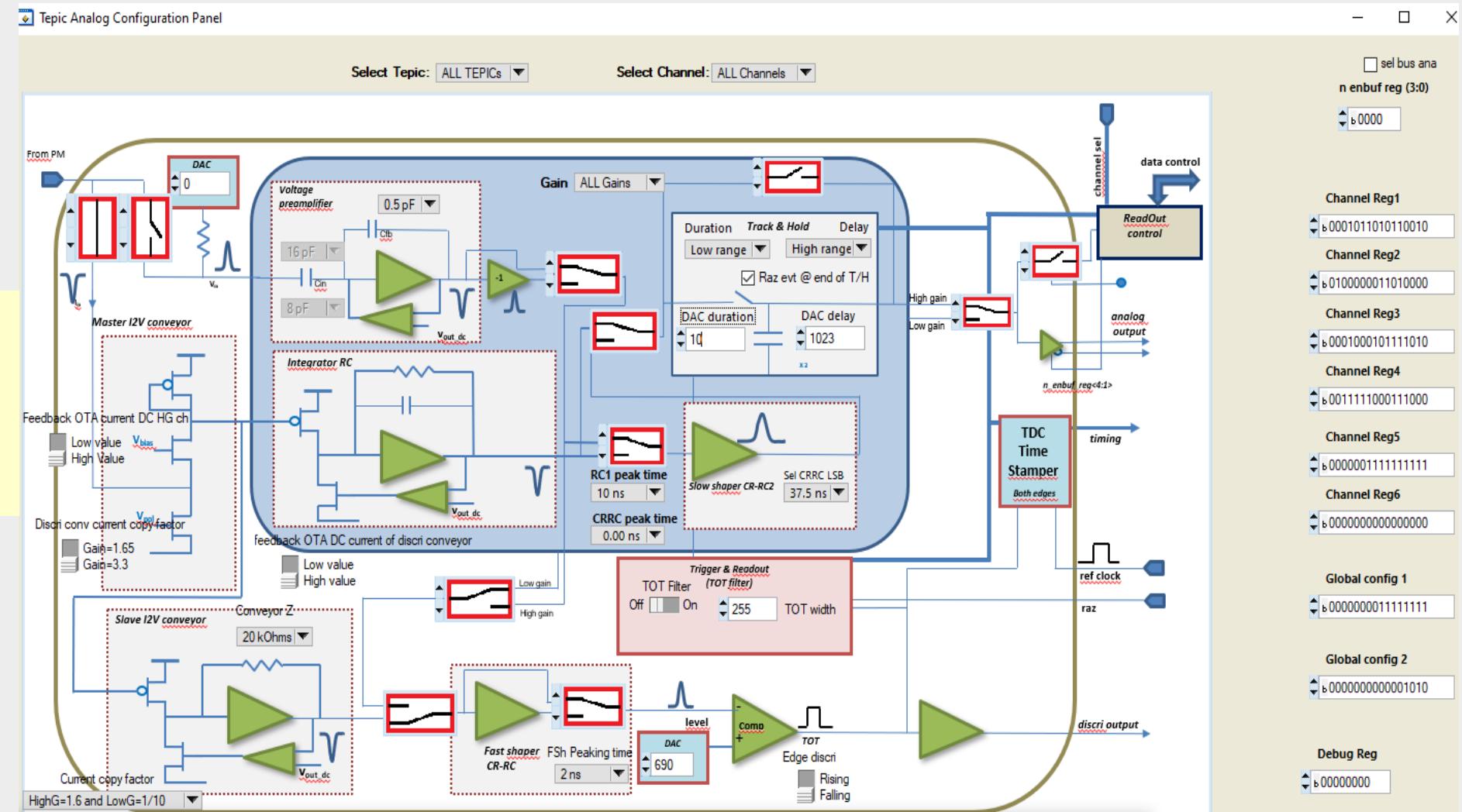

# Logiciel de contrôle et d'acquisition (1/3)

- Utilisation de l'environnement LabWindows/CVI, en langage C

Panneau graphique de la partie analogique qui reprend la schéma de principe :

→ Facile d'utilisation et de compréhension

Interface graphique pour le contrôle de la partie analogique.

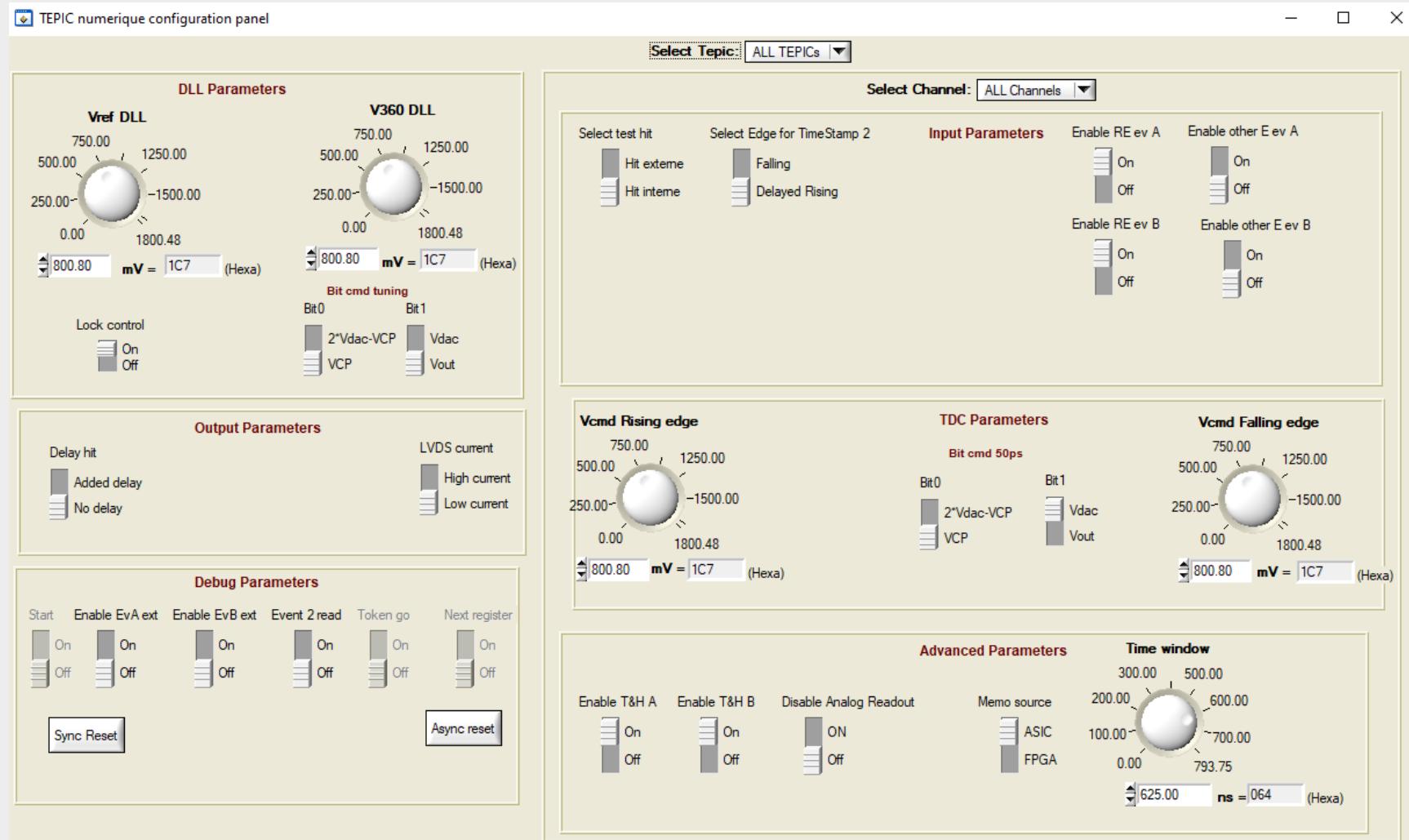

# Logiciel de contrôle et d'acquisition (2/3)

Panneau de configuration de tous les paramètres

de la partie numérique du circuit

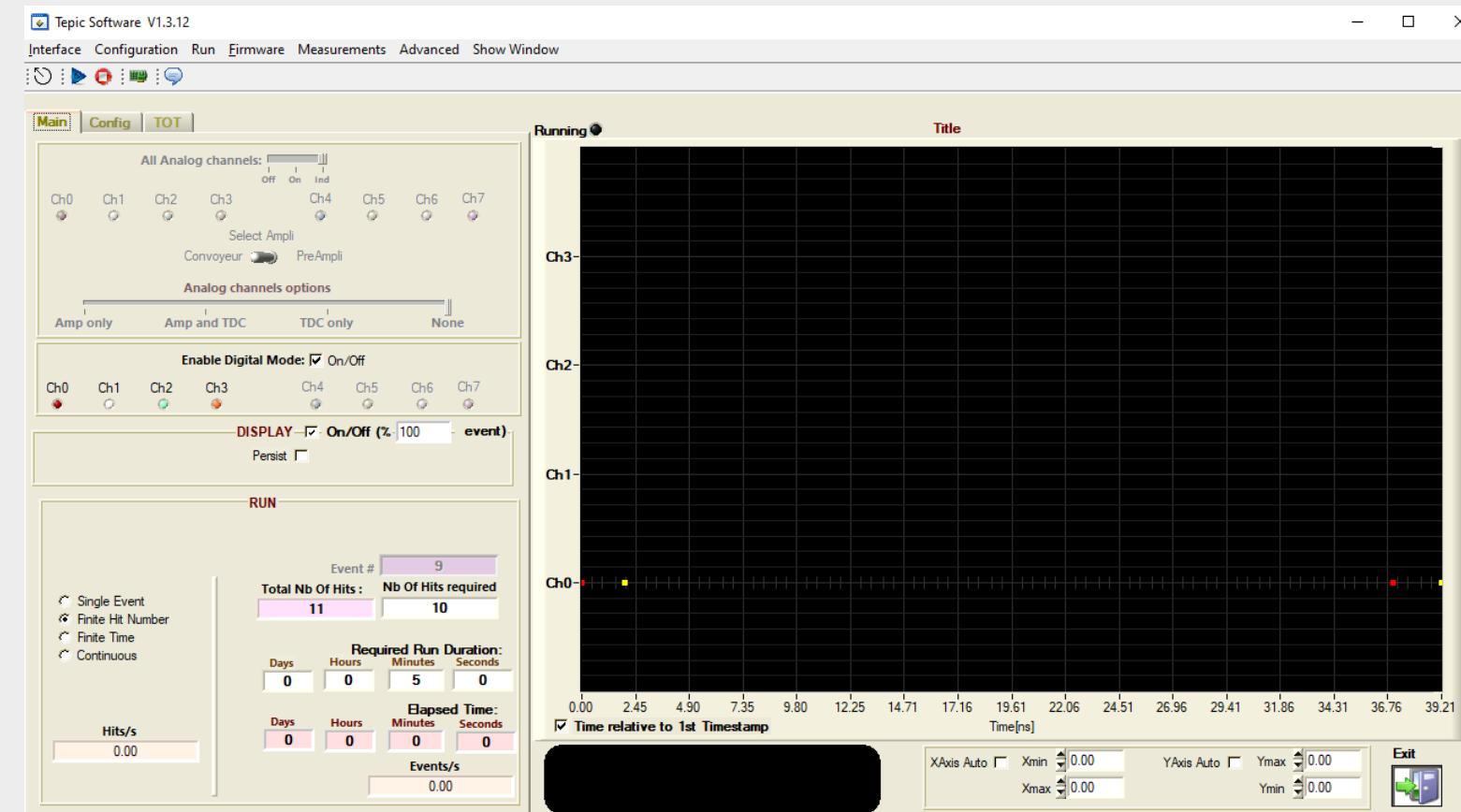

# Logiciel de contrôle et d'acquisition (3/3)

Panneau principal avec visualisation des données

« temps »

Panneau d'histogramme de mesure de temps

et StripChart

# Principe de Fonctionnement d'un TDC à DLL

- But du TDC:** Capturer le temps d'arrivée d'un signal numérique, comme un « **chronomètre** »

Dans le circuit, il y a deux manière d'envoyer un signal numérique au TDC:

1. Hit provenant de la partie analogique, à la sortie du discriminateur.

1. Hit provenant de l'entrée 'Test' du circuit connectée à une entrée externe de la carte

A l'arrivée du signal numérique :

1. On mémorise l'état du **compteur grossier** ( pas de 6,25 ns, si horloge d'entrée = 160 MHz)

2. On mémorise l'état de la **DLL** (qui donne le **pas fin**)

# Fonctionnement de la DLL (Delay Line Loop)

La ligne à retards (DLL) est **asservie à l'horloge** qui est à son entrée:

- On force, grâce au **comparateur de phase et à la pompe de charge**, le fait que la **somme de tous les retards** soit égale à **une période horloge**. Chaque « retard » est alors égal à :  $\frac{T_{Horloge}}{\text{nombre de retards de la DLL}}$

- La DLL permet donc d'**interpoler** à l'intérieur du pas de l'horloge et donner un **pas fin** (~97ps).

Compteur grossier dans le TEPIC (sur 16 bits)

Le Comparateur de phase + pompe de charge

La ligne à retards rebouclée : 64 portes NAND.

$$\tau_{\text{ligne}} = T_{\text{Horloge}} = 6,25 \text{ ns}$$

$$\tau_{\text{cellule théo}} = \frac{T_{\text{Horloge}}}{64} \sim 97 \text{ ps}$$

Compteur grossier dans le FPGA (sur 48 Bits): il étend le champ de bits du compteur grossier du TEPIC

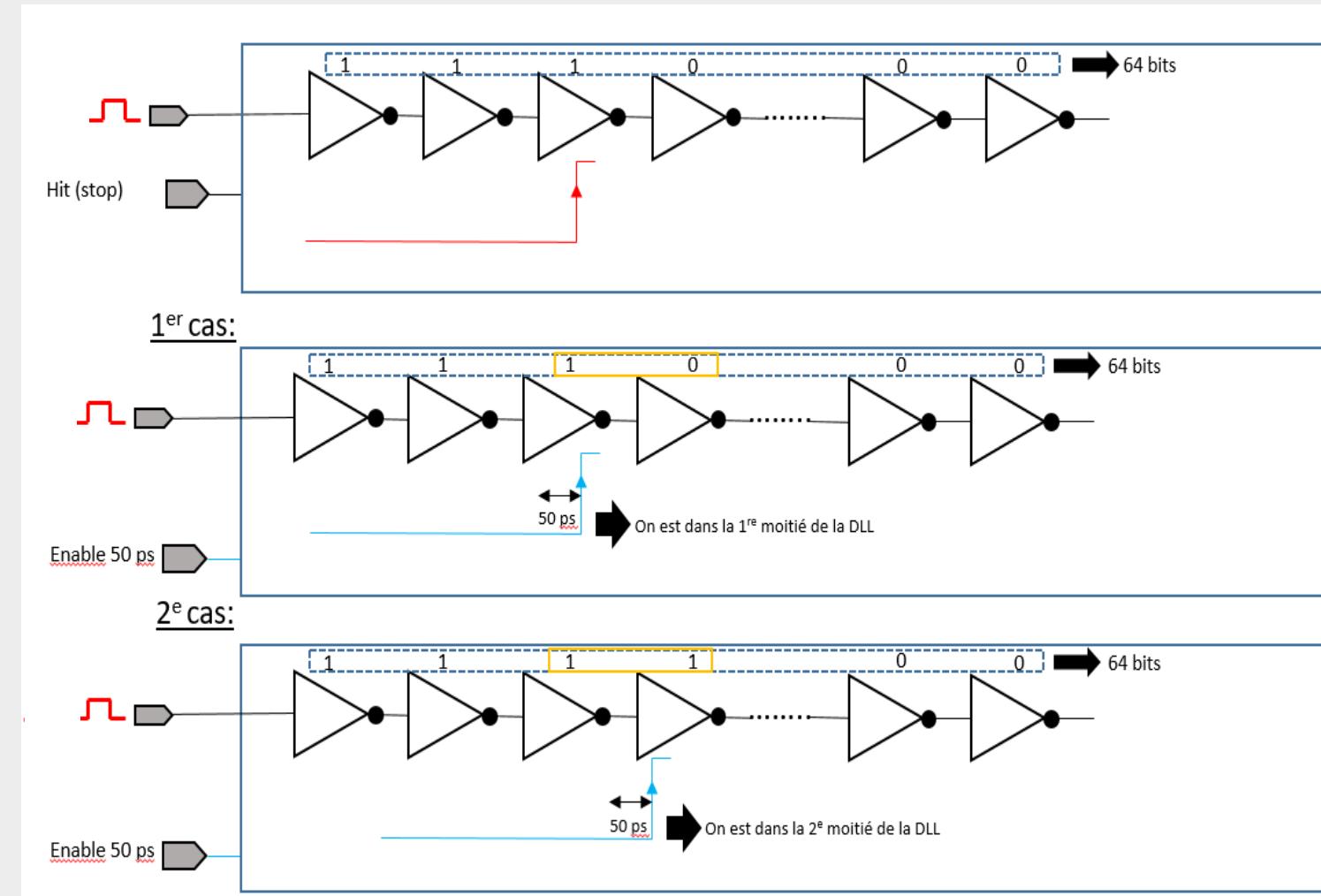

# Principe du « double hit » du TDC de TEPIC

But : affiner encore plus le pas de la DLL ?

On **retarde le signal** numérique avec un **délai fixe** égal à peu près à  $\sim 50$  ps (moitié du pas de la DLL) et on **recapture** une deuxième fois l'état de la DLL.

**Etat de la DLL = l'endroit où se trouve l'horloge au moment de la capture.**

- 1<sup>er</sup> cas:

si  $t_{1\text{ere capture}} \in [0; 50]$  ps, de la **cellule i**

$\Rightarrow t_{2\text{e capture}} \in [50; 100]$  ps, de la **cellule i**

Dans ce cas, l'état de la DLL **ne change pas** entre les deux captures

- 2<sup>e</sup> cas:

si  $t_{1\text{ere capture}} \in [50; 100]$  ps, de la **cellule i**

$\Rightarrow t_{2\text{e capture}} \in [0; 50]$  ps, de la **cellule i + 1**

Dans ce cas, l'état de la DLL **change** entre les deux captures

Description du principe de « double hit » ou double échantillonnage de la DLL

Grâce au double échantillonnage de la DLL, on descend le pas du TDC à  $\sim 50$  ps!

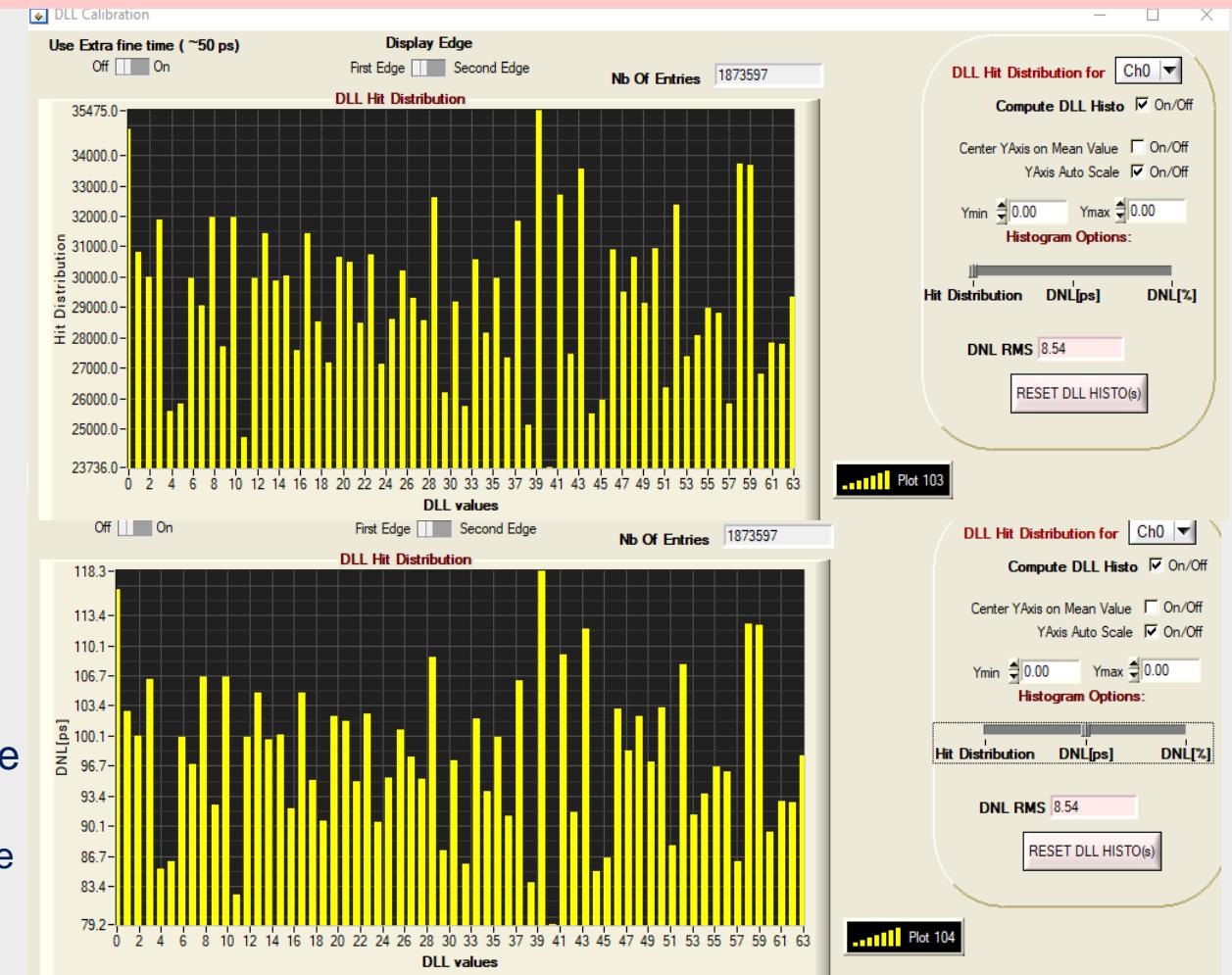

# Calibration de la DLL : mesure de la DNL

Au vu des disparités liées à la gravure du silicium, ainsi que des dispersions des tensions d'alimentation dans le circuit, toutes les cellules à retard n'ont pas un retard **parfaitement égal au retard théorique** attendu qui est:  $\tau_{cellule \text{ théo}} = 97,65 \text{ ps} (\sim 100 \text{ ps})$

=> On appelle la disparité dans la valeur des retards de la DLL : **la Non Linéarité Différentielle (DNL)**

- Pour estimer le retard de chaque cellule expérimentalement on utilise une **méthode statistique**:

- Envoi de hits asynchrones de l'horloge du circuit provenant d'un générateur

- Le taux de remplissage de chaque cellule est directement proportionnel à la valeur de son retard: en effet plus le retard est grand, plus la cellule sera touchée et inversement.

- On réalise un **histogramme** représentant la distribution des hits en fonction de la cellule à retard touchée.

- On traduit cette distribution en « picosecondes », sachant que la somme de tous les retards doit être égale à  $T_{Horloge}$

- On en déduit le délai de chaque cellule à partir de son nombre de hits enregistrés

$$\tau_{cellule \text{ } i \text{ exp}} = \frac{\text{Nb hits reçus par cellule } i}{\text{Nb hits total sur DLL}} \times T_{Horloge}$$

Histogramme de la distribution des hits reçus sur chaque cellule de la DLL (en nombre de hits et en ps) RMS : 8, 5ps !!

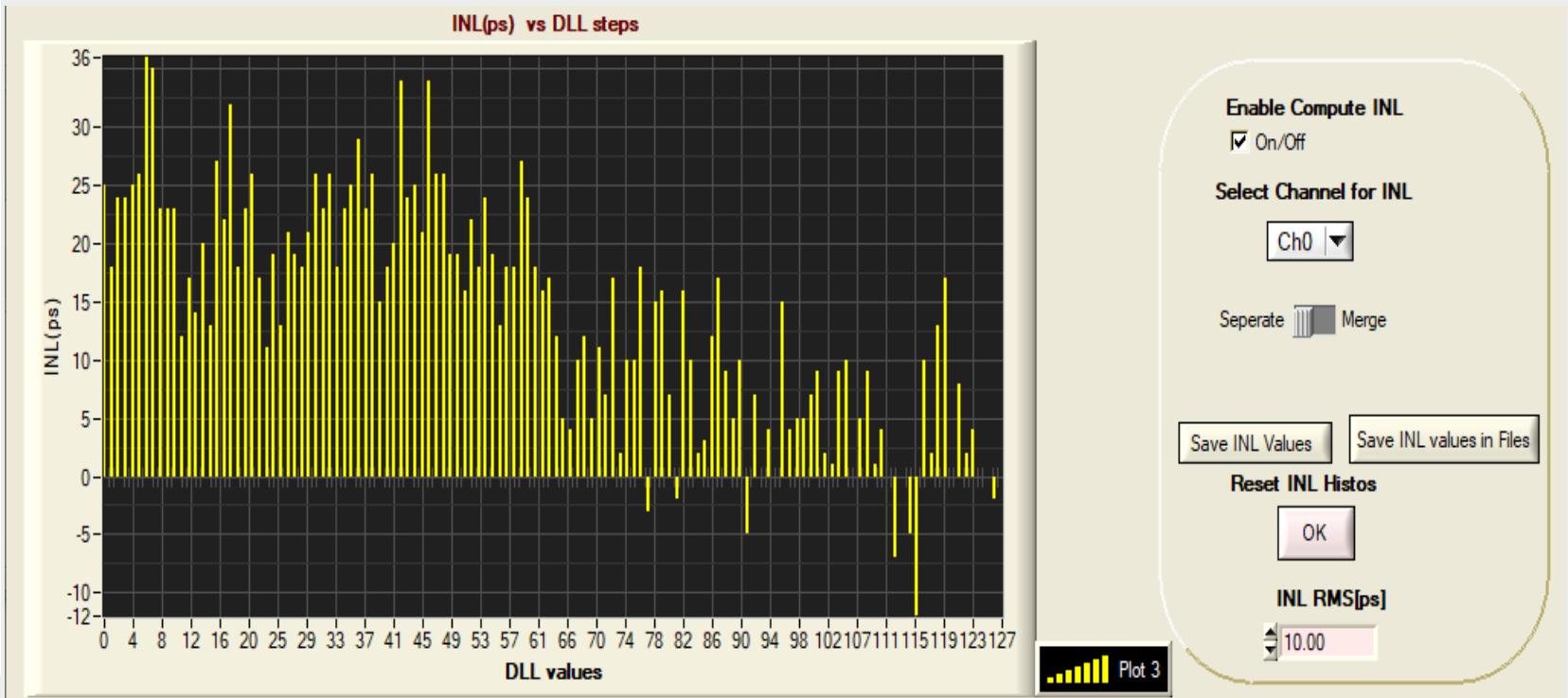

# Calcul de l'INL (Non linéarité Intégrale)

- Comme la somme des retards de chaque cellule doit valoir  $T_{horloge}$ , en théorie on doit avoir pour la cellule 0 :

$$Delay_{cellule\ 0\ theo} = \frac{T_{horloge}}{64} \quad (6)$$

Or on mesure une certaine DNL (ou délai) en réalité, on en déduit donc la correction à apporter :

$$INL_{cellule\ 0} = \frac{T_{horloge}}{64} - DNL_0 \quad (7)$$

- Pour la cellule 1, on a un délai théorique de :

$$Delay_{cellule\ 1\ theo} = 2 \cdot \frac{T_{horloge}}{64} \quad (8)$$

- Pour la correction de la cellule 1, on doit rajouter la correction de la cellule 0 (cumul des erreurs) :

$$INL_{cellule\ 1} = 2 \cdot \frac{T_{horloge}}{64} - (DNL_0 + DNL_1) \quad (9)$$

- On peut donc inférer une formule par récurrence pour chaque cellule de la ligne à retard :

$$\forall n \in [[0; 63]], INL_{cellule\ n} = (n+1) \cdot \frac{T_{horloge}}{64} - \sum_{k=0}^n DNL_k \quad (10)$$

Si le pas de 50 ps est activé :

$$\forall n \in [[0; 127]], INL_{cellule\ n} = (n+1) \cdot \frac{T_{horloge}}{128} - \sum_{k=0}^n DNL_k \quad (11)$$

Cette somme représente une approximation de l'aire sous la courbe de l'INL, c'est donc une approximation de l'intégrale.

- Grâce aux délais mesurés pour chaque cellule de la DLL, on **calcule la correction à apporter** à chaque mesure de temps, en fonction de la cellule à retard touchée.

➤ Cela revient à calculer la **Non Linéarité Intégrale (INL)**

*INL (ps) en fonction du numéro de la cellule à retard de la DLL,

RMS ~ 10ps !*

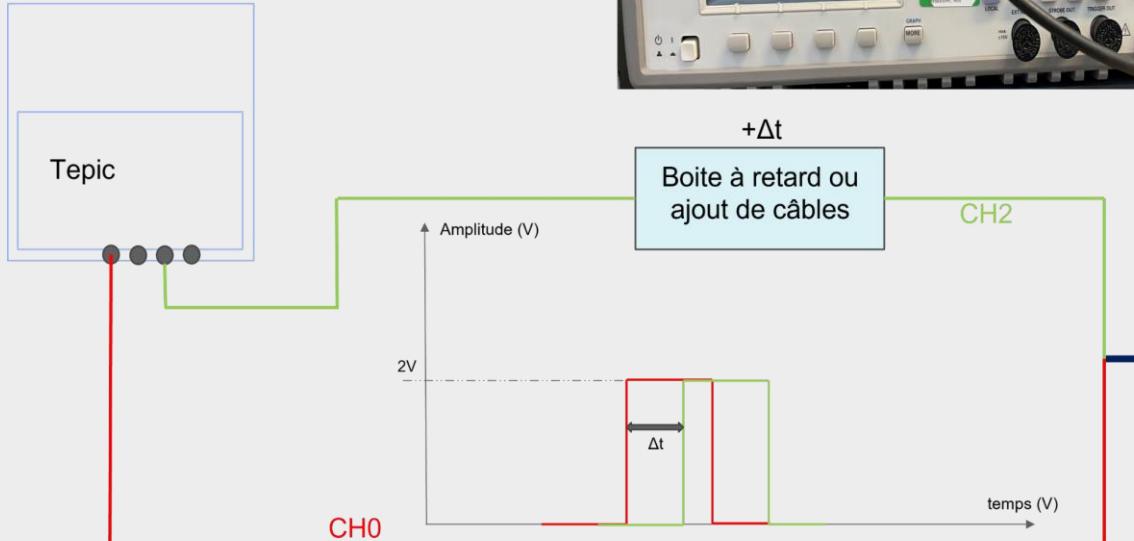

# Protocole de mesure de la résolution en temps du TDC

Caractérisation du TDC : mesure de la résolution en temps, grâce à la mesure de  $\Delta t$  entre deux signaux.

| Paramètres du signal |     |

|----------------------|-----|

| Amplitude(V)         | 4   |

| f (kHz)              | 100 |

| T monté(ns)          | 0,8 |

| T descente (ns)      | 0,8 |

| Largeur (ns)         | 100 |

Schéma du banc de mesure de  $\Delta t$ .

- Envoi d'un pulse venant du générateur (asynchrone par rapport à l'horloge du TEPIC)

- Ce pulse est divisé en deux et envoyé sur deux câbles de **longueur différente**. (afin de créer un **différence de temps** sur l'arrivée des signaux)

- On, envoie ces pulses sur les entrées numériques de la carte de test.

- Cela induit un retard de propagation et donc un  $\Delta t$  entre les deux signaux.

- Production de l'histogramme des mesures pour différentes valeurs de  $\Delta t$

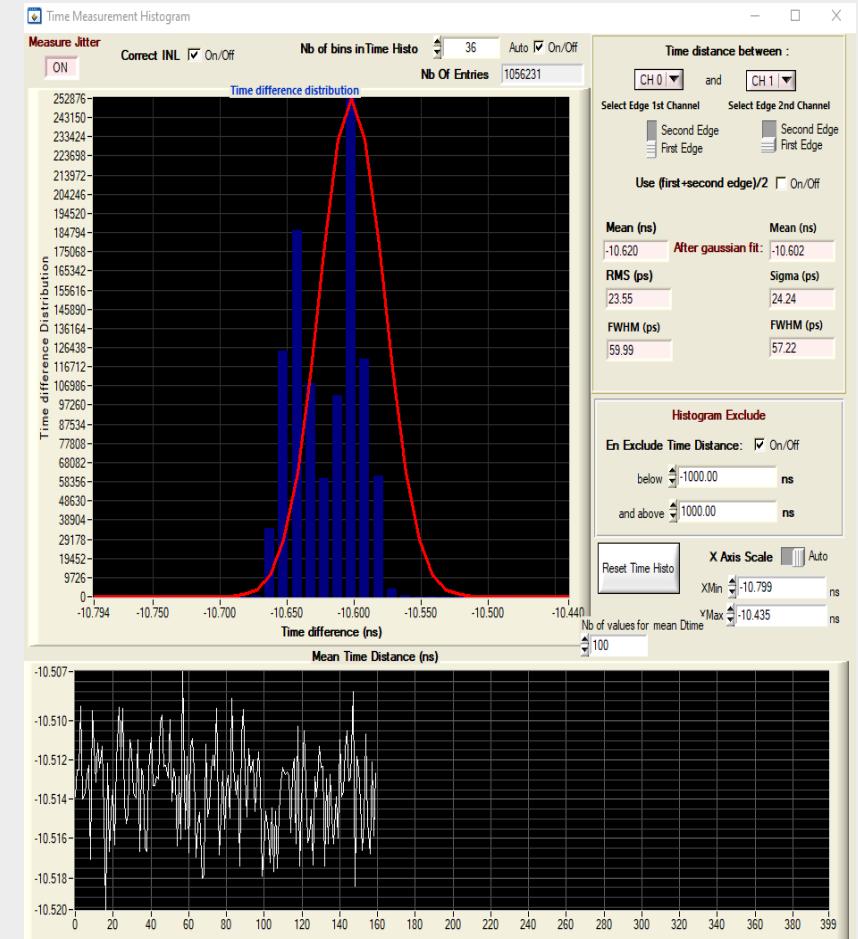

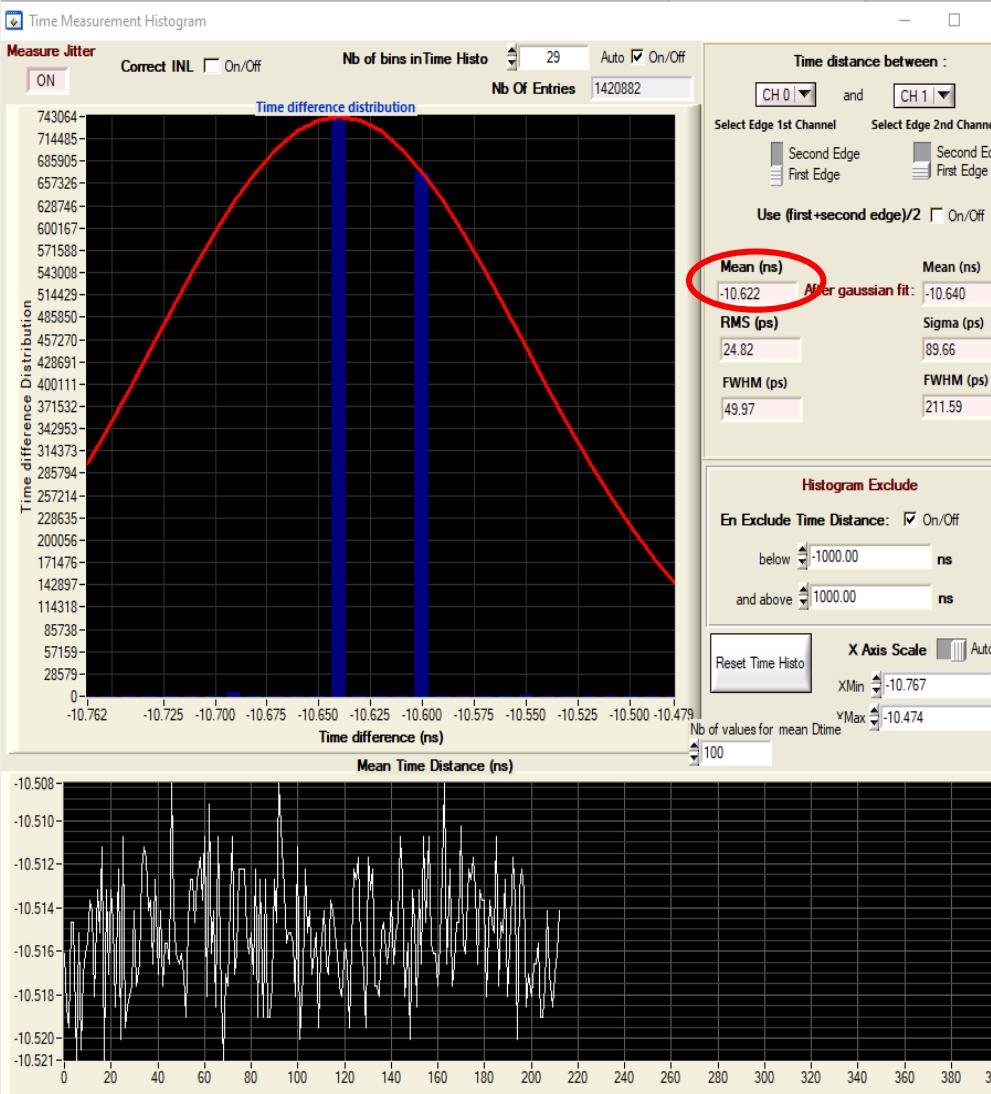

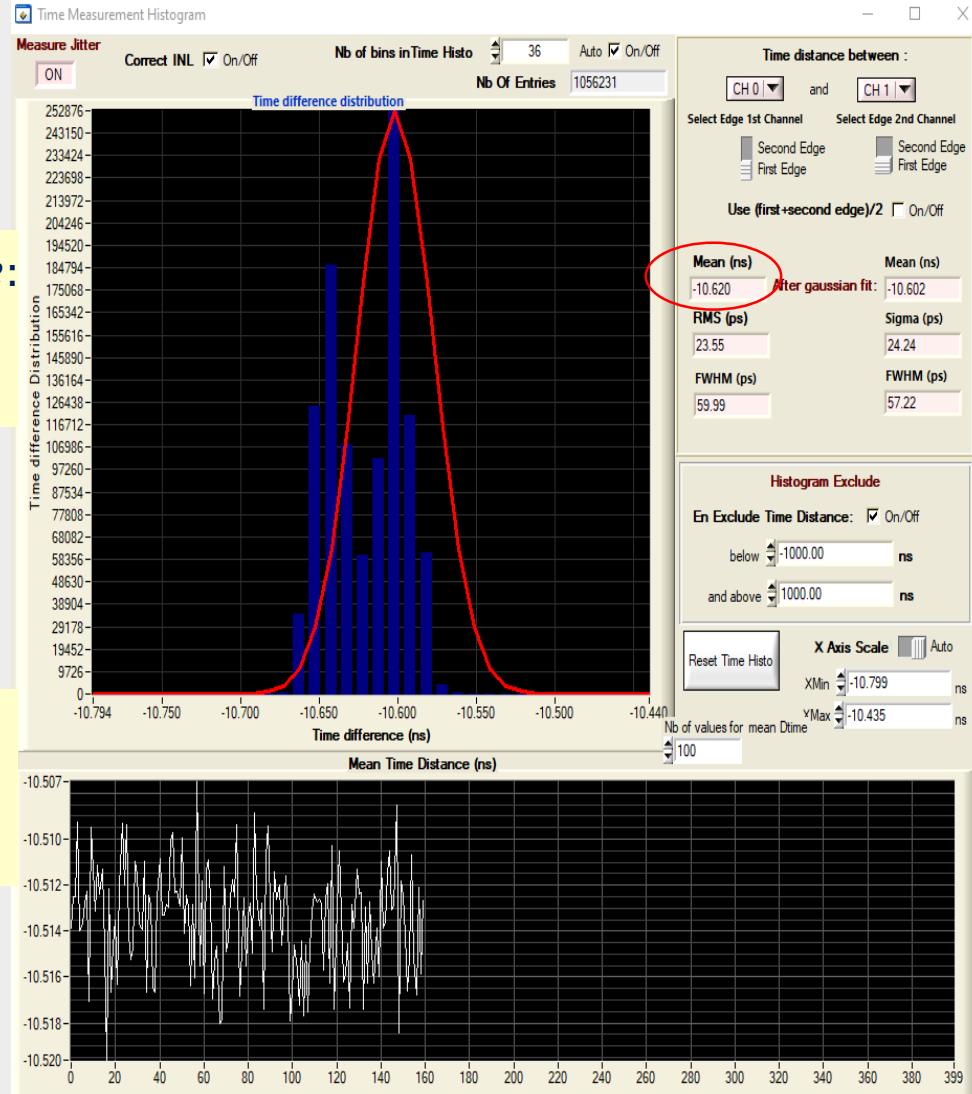

# Exemple d'Histogramme pour $\Delta t \sim 10\text{ns}$

Histogramme de la mesure de  $\Delta t$ , sans correction d'INL.  $\rightarrow$  RMS 24,8 ps

Pour une mesure sur une voie:

$$\text{Résolution théorique: } \frac{LSB}{\sqrt{12}} \approx 14,4 \text{ ps}$$

Pour une différence de temps entre deux voies :

$$\text{Résolution théorique } \frac{LSB}{\sqrt{12}} \times \sqrt{2} \approx 20 \text{ ps}$$

Histogramme de la mesure de  $\Delta t$ , avec correction d'INL. RMS  $\rightarrow$  23,5 ps

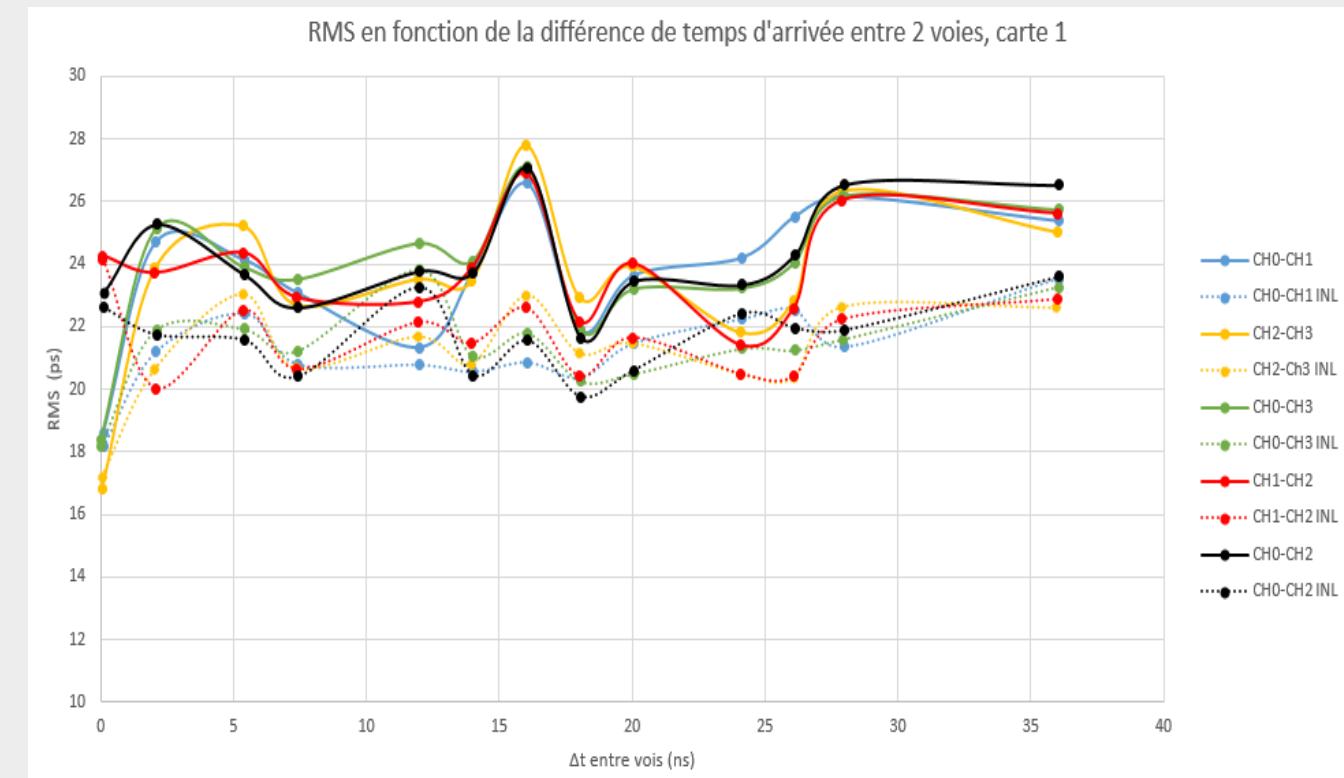

# Résolution du TDC (RMS) en fonction de $\Delta t$

- Le RMS représente l'**écart type** de  $\Delta t$  (ou « jitter » de la mesure).

- On observe une diminution du RMS quand on utilise la correction INL (entre 1 et 6ps)

- On s'approche de la valeur théorique (~20 ps rms)

- On voit que même sans correction la mesure de temps est déjà très bonne (max 28 ps), ce qui traduit le fait que les cellules à retards sont très proches du délai théorique (~100 ps) et très stables.

$$\sigma(RMS) = \sqrt{\frac{\sum(x_i - \bar{x})^2}{N}}$$

RMS de la différence de temps en fonction de  $\Delta t$  avec et sans correction d'INL

# Conclusion

- J'ai travaillé pendant sur la caractérisation du circuit TEPIC, ce qui m'a permis de comprendre une chaîne électronique complète : de l'étage de pré-amplification, à la mesure de temps et l'acquisition de données.

- Les performances du TDC de TEPLIC sont excellentes: entre 18 – 24 ps rms sur la mesure de différence de temps.

- Ce TDC a également été implémenté en 130 nm dans un autre ASIC, appelé DiamASIC (projet R&T transverse IN2P3) dédié à la lecture de détecteurs diamants. Un circuit intégrant l'ensemble de la chaîne : amplification + discriminateur + TDC, sera prochainement soumis ( en 2024)

# Merci de votre attention